RayeR wrote on 2024-01-03, 17:29:

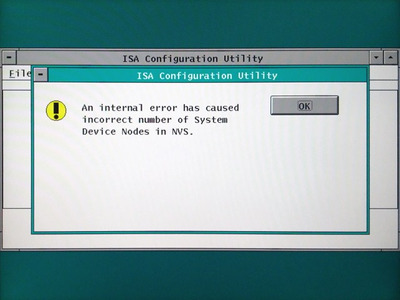

Do you also use shared IRQ with LPT or do you have IRQ exclusive only for soundcard? Any idea how to alter the PCI PnP mechanism to reserve some legacy IRQ? It's probably done in early phase after power up, far before LPC bridge is initialized so PnP enumerator has no chance to see PnP devices on ISA bus. For me it's just a blackbox, I never get deep in how PnP enumeration works...

I don't think new motherboards offer such option to control IRQ assignments in BIOS. All IRQs are free to be claimed by any PCI device.

From my experience ISA PnP is in most cases the same as legacy ISA if you need the card on a specific IRQ and/or DMA -- you need to reserve the resources in BIOS first so others would not try to claim (no guarantee this will work on every chipset, however).

Such use case is only important for using sound cards in DOS but not in other use cases (Windows, for example). Just that depending on hardware design the card may only be able to choose specific IRQs and will fail to initialize if all IRQs it could use are claimed by others.

RayeR wrote on 2024-01-03, 17:29:

But in my case I replaced the A00-AFF (SAPPHISA default ) by 660 and it works. So any program could use A00-AFF when I disabled it before running ESSCFG, even ESSCFG itself.

Maybe one could always interact with a card's control port if known, and doesn't really have to use the 279/A79 ports (ISA PnP).

RayeR wrote on 2024-01-03, 17:29:

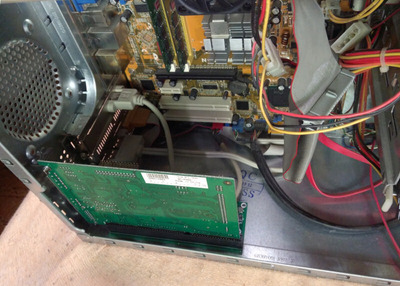

Did you find out how TPU interfere with LPC bridge? I think you wrote that you tried both LPC bridge IO ranges so it couldn't be IO conflict. Even if so I think at least superIO chips use some magic byte to valid access so maybe even 2 different superIO may not interfere at same IO address, not sure... If it's possible can you detach the TPU LPC off the bus (lifting up a pin or so)?

I'm not sure. On that board (with TPU), the Fintek bridge is detected, but most of the configuration registers return FF instead of the expected default.

What those TPU chips really control is unclear, and it's not trivial to detach them from the bus. I would have to locate and detach every LPC pin (LAD0-LAD3, LFRAME#, etc.). I can't find much info about the TPU chip itself, however...