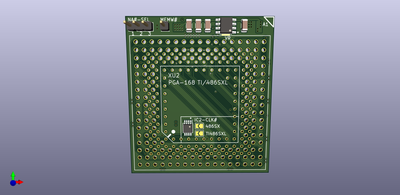

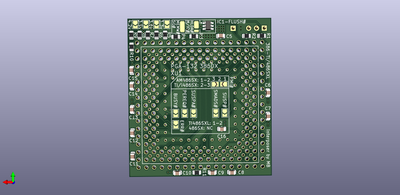

This is my version of the interposer.

It's designed to be compatible with the TI486SXL, TI486SXL2, as well as Intel & AMD 486SX, 486SX2 with jumper changes.

The design is untested as the sockets won't arrive until April, however it IS finished and possible to build using other sockets.

I don't have anything left to update on it (updated 12 Mar 2024), so I'm posting it now. Anyone can build and test it, minus the sockets, or wait until ~April to see me build & test it.

Images attached: 3D renders and the 168pin press-fit socket.

Gerber files are also attached for PCB manufacture.

PCB design requirements:

Length: 51.562

Width: 46.736

Layers: 4

Material: FR-4. 1.6mm

Min track/spacing: 6mil / 0.15mm

Min hole size: 0.3mm

Edge connector: no

Finished copper: 1oz

Inner copper: 1oz

Vias: No blind/buried vias present

Bill Of Materials (BOM):

Resistors:

-R1, R3, R5, R10 - 20k - RT0805DRD0720KL

-R2, R11 - 100r 0.5W Thick Film - CRCW0805100RFKEAHP

-R4 - 4.42k Thin Film (<=0.5% tolerance) - RT0805BRD074K42L

-R6, R7, R8, R9 - 2.2k Thin Film (<=0.5% tolerance) - RT0805BRD072K2L

Capacitors:

-C1 10uF - CL31B106KAHNFNE

-C2, C3, C4 - 3.3uF - CL31B335KAHVPNE

-C5 to C16 inclusive - 0.1uF - C0805C104K5RACTU

VR: AP7363-SP-13 (SO-8EP)

IC1: SN74LVC1G58DBVR (SOT-23-6)

IC2 (CLK): 74LVC2G74 (SOT-505-2)

XU1: 132pin 550-10-132-14-071101

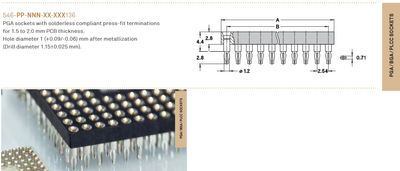

XU2: 168pin press-fit 546-83-168-17-101136

Sockets are only available from mouser at a high price. I didn't want to hand-solder rows, so the 132pin is a complete socket interconnect, and the 168pin is a press-fit (image attached). The availability currently is 23 for the 168pin, and 29 for the 132pin sockets, available on 19 April 2024. If they run out you need to wait another four months.

XU1: 132pin (550-10-132-14-071101): https://au.mouser.com/ProductDetail/Preci-dip … vOFry3q6Q%3D%3D

XU2: 168pin press-fit (546-83-168-17-101136): https://au.mouser.com/ProductDetail/Preci-dip … xAJb6r7AQ%3D%3D

Other info:

-Voltage is selected by the solder jumpers on the back. 3.3v, 3.6v, 3.9v, 4.2v. If none are jumpered, voltage is 4.5v. If more than one is jumpered, the lowest voltage is used.

-Solder pads on reverse side that operate FLUSH#: HLDA/M-IO and MEMW/SO, and are only required if you use them. The smaller pad under HLDA/M-IO is HLDA (CPU), used for testing 486sx CPUs that don't have MEMW and don't respond to Cyrix software.

-MEMW# single large through-hole is connected directly to the CPUs MEMW#.

-NA-SEL# default is jumpered 1-2 or NC.

-IC2 (CLK) is only required if testing a 486SX CPU.

-Underneath the VR/Volt Reg, a 5v pad is close-by the output in case the VR isn't used, so it can be solder-jumpered to output 5v. If 5V is used C1-10uF isn't required.

-If the VR/Volt Reg is used, the ground pad underneath needs to be soldered.

To configure for Intel & AMD 486SX. (NMI is the only difference between Intel & AMD):

1) 5V: Bypass Volt Reg if required.

2) CLK/CLK2# select. 486SX or TI486SXL.

3) BUSY#: 486SX: NC. TI486SXL: 1-2.

4) SUSP#: 486SX: NC. TI486SXL: 1-2.

5) SUSPA#: 486SX: NC. TI486SXL: 1-2.

6) SMADS#: 486SX: NC. TI486SXL: 1-2.

7) PEREQ#: 486SX: NC. TI486SXL: 1-2.

8 ) ERROR#: 486SX: NC. TI486SX): 1-2.

9) NMI#: AM486SX: 1-2. i486SX/TI486SXL: 2-3.

10) MEMW# (large through-hole on interposer): NC.

11) Use FLUSH# IC & pads on reverse side of interposer. The smaller pad under HLDA/M-IO is HLDA (CPU).

-a) If HOLD# is always sent to the CPU during DMA/master cycles, solder the larger pad HLDA/M-IO to the smaller pad HLDA (CPU), and solder MEMW# from the ISA bus.

-b) If HOLD# is NOT always sent to the CPU during DMA/master cycles, solder HLDA# and MEMW# from the ISA bus/Cache-Memory Controller. Leave the smaller pad unconnected.

Intel/AMD 486DX & 586 may work using AM486SX settings. FERR# and IGNNE# are not connected.

9/10 Jan 2024: Updated solder jumper pads for CPU. Support for AM486SX.

15 Jan 2024: Updated resistor values for voltage selection. 3.3v, 3.6v, 3.9v, 4.2v. No jumper = 4.5v.

12 Mar 2024: Cosmetic update. Updated note about smaller solder pad on reverse side (see note in 'other info' above).

May 2024: PGA-168 footprint update. VCC cap vias. (pending)