Reply 381 of 459, by Keatah

Graphics chip not displaying name..

Reply 382 of 459, by Schule04

- Rank

- Member

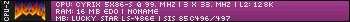

Intel 386SX 16MHz

With 1 waitstate:

With 0 waitstate:

Reply 383 of 459, by CuPid

Reply 384 of 459, by Schule04

- Rank

- Member

It's interesting. Some clicks take minutes, but for the most part it's surprisingly fast. And this is with only 5MB RAM. I guess having an accelerated graphics card helps a lot

Reply 385 of 459, by Woody72

- Rank

- Newbie

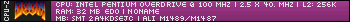

Here are my Windows 98SE results. Pretty vanilla system so no surprises here:

Modern PC: i7-9700KF, 16GB memory, RTX 3060. Proper PC: Pentium 200 MMX, 128MB EDO memory, GeForce2 MX(200).

Reply 386 of 459, by mwdmeyer

- Rank

- Oldbie

Hi CuPid,

Thank you for releasing this program.

I have a question for you about the inbuilt benchmarks. Do these use MMX or 3dnow? I'm testing a wide range of CPUs and interested to know how the benchmark functions.

Here are some examples of the benchmarks: https://www.vogonswiki.com/index.php/Super_So … ge_Edition_1.03

Thanks

Vogons Wiki - http://vogonswiki.com

Reply 387 of 459, by CuPid

- Rank

- Member

mwdmeyer wrote on 2021-04-12, 08:50:Hi CuPid, […]

Hi CuPid,

Thank you for releasing this program.

I have a question for you about the inbuilt benchmarks. Do these use MMX or 3dnow? I'm testing a wide range of CPUs and interested to know how the benchmark functions.

Here are some examples of the benchmarks: https://www.vogonswiki.com/index.php/Super_So … ge_Edition_1.03

Thanks

hello !

No, the bench does not use any instruction set.

Interesting work on merging the results !

Reply 388 of 459, by Schule04

- Rank

- Member

IBM 486SLC2 @66MHz

L1 Cache should be 16KB, and there is 128K L2 cache which is not detected.

Socket type should be QFP-100, the same as the 386SX chips.

Reply 389 of 459, by Repo Man11

- Rank

- l33t

On my Epox MVP3G-M I discovered that if ACPI is enabled in the CMOS settings, CPU Z locks up Windows 98 and I have to hit reset. With ACPI disabled version 1.03 works fine.

After watching many YouTube videos about older computer hardware, YouTube began recommending videos about trains - are they trying to tell me something?

Reply 390 of 459, by CuPid

- Rank

- Member

Schule04 wrote on 2021-04-25, 00:41:IBM 486SLC2 @66MHz L1 Cache should be 16KB, and there is 128K L2 cache which is not detected. Socket type should be QFP-100, the […]

IBM 486SLC2 @66MHz

L1 Cache should be 16KB, and there is 128K L2 cache which is not detected.

Socket type should be QFP-100, the same as the 386SX chips.IMG_20210425_011331b.jpgIMG_20210425_011416b.jpg

Yes the detection if the IBM 486SLC is problematic under Windows 9x. I did not find a reliable method yet.

So the program assumes this is a 486 w/o FPU (an SX then), and is wrong on everything (cache, clock speed, socket ...).

Reply 391 of 459, by NostalgicAslinger

- Rank

- Member

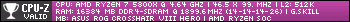

Pentium MMX 200 overclocked to 300 MHz (from 66MHz to 100 MHz FSB) with default P55C 2.8V VCore, also Prime stable.

Reply 392 of 459, by ultra_code

- Rank

- Oldbie

the_ultra_code wrote on 2020-10-29, 21:42:Hello! […]

Hello!

I noticed this little project of yours, so I decided I'd check out Vintage Edition v1.02 on my Pentium III-S 1.4Ghz rig to see how it stacks up against one of the last versions of CPU-Z supported by Win98SE that I know of (v1.57). I will say, I love the improvements to the readability of the text (I increased the size of the text in the .inf file for v1.57 for the text to be more readable) as well as some minor layout improvements. I also see that some more information is being displayed in the VE than in the older version. Keep up the great work!

To further help, I did notice one regression between v1.57 and VE v1.02 that I would like to report. It has to do with the VE not reporting my mainboard's "LCPIO", whatever that is. 😀

Here's the missing information from the VE report that's in the report from v1.57:

LPCIO Vendor AsusTekLPCIO Model AS99127FLPCIO Vendor ID 0x5CA3LPCIO Chip ID 0x59LPCIO Revision ID 0x53Config Mode I/O address 0x2EConfig Mode LDN 0xBConfig Mode registers00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F00 FF FF FF FF FF FF FF 0B FF FF FF FF FF FF FF FF10 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF20 59 53 FF FE 80 00 00 FF 00 0C 7C F0 1F 00 00 FF30 00 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF40 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF50 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF60 00 00 FF FF FF FF FF FF FF FF FF FF FF FF FF FF70 00 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FFI have included both reports as well as the above screenshot in the zip file attached for your assistance. If there's anything else you need from me, feel free to ask.

Just checked with the latest vintage edition - still displaying the same issue of not displaying LPCIO:

Reply 393 of 459, by red-ray

- Rank

- Oldbie

the_ultra_code wrote on 2021-05-01, 20:55:I have included both reports as well as the above screenshot in the zip file attached for your assistance.

I just looked at the SPD in WIN98SE_TUSL2-C_1-57.txt and it's reporting Data width 16448 bits which must be wrong, further the checksum is incorrect so I suspect your SPD data is wonky.

Reply 394 of 459, by ultra_code

- Rank

- Oldbie

red-ray wrote on 2021-05-02, 11:19:the_ultra_code wrote on 2021-05-01, 20:55:I have included both reports as well as the above screenshot in the zip file attached for your assistance.

I just looked at the SPD in WIN98SE_TUSL2-C_1-57.txt and it's reporting Data width 16448 bits which must be wrong, further the checksum is incorrect so I suspect your SPD data is wonky.

IDK. This is a newer module from the mid-2000s I think. It is MemTest stable.

Reply 395 of 459, by red-ray

- Rank

- Oldbie

the_ultra_code wrote on 2021-05-02, 21:24:IDK. This is a newer module from the mid-2000s I think. It is MemTest stable.

MemTest does not test the SPD. I looked some more and what CPUZ reported is:

Data width 16448 bits

Correction None

Registered no

Buffered no

EPP no

XMP no

JEDEC timings table CL-tRCD-tRP-tRAS-tRC @ frequency

JEDEC #1 2.0-2-2-6-n.a. @ 133 MHz

JEDEC #2 3.0-2-2-6-n.a. @ 133 MHz

DIMM # 1

SPD registers

-- 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

00 80 08 04 0D 0A 02 40 40 01 75 54 00 82 08 00 01

The 40 at offset 07 should be 00 so either your SPD is corrupt or CPUZ misread that byte. SIV32 does not report SPD in W98, but if you can boot NT4, W2K or WXP it will. HWiNFO32 should report SPD on W98.

Reply 396 of 459, by ultra_code

- Rank

- Oldbie

red-ray wrote on 2021-05-03, 08:52:MemTest does not test the SPD. I looked some more and what CPUZ reported is: […]

the_ultra_code wrote on 2021-05-02, 21:24:IDK. This is a newer module from the mid-2000s I think. It is MemTest stable.

MemTest does not test the SPD. I looked some more and what CPUZ reported is:

Data width 16448 bits

Correction None

Registered no

Buffered no

EPP no

XMP no

JEDEC timings table CL-tRCD-tRP-tRAS-tRC @ frequency

JEDEC #1 2.0-2-2-6-n.a. @ 133 MHz

JEDEC #2 3.0-2-2-6-n.a. @ 133 MHz

DIMM # 1

SPD registers

-- 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

00 80 08 04 0D 0A 02 40 40 01 75 54 00 82 08 00 01The 40 at offset 07 should be 00 so either your SPD is corrupt or CPUZ misread that byte. SIV32 does not report SPD in W98, but if you can boot NT4, W2K or WXP it will. HWiNFO32 should report SPD on W98.

If you are curious, I got a HWINFO32 report and debug file from the system.

Reply 397 of 459, by red-ray

- Rank

- Oldbie

the_ultra_code wrote on 2021-05-05, 04:19:I got a HWINFO32 report and debug file from the system.

It looks like CPUZ messed up the SMBus SPD reading as looking in the .DBG file SPD offset 07 is 00 which is what it should be, further the SPD checksum is correct.

SMB:0:50

..... 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 0123456789ABCDEF

------------------------------------------------------------------------

0000: 80 08 04 0D 0A 02 40 00 01 75 54 00 82 08 00 01 € @ÿuTÿ‚ÿ

It would not surprise me if you re-ran the CPUZ save and the value was then as it should be.

Reply 398 of 459, by ultra_code

- Rank

- Oldbie

red-ray wrote on 2021-05-05, 09:14:It looks like CPUZ messed up the SMBus SPD reading as looking in the .DBG file SPD offset 07 is 00 which is what it should be, f […]

the_ultra_code wrote on 2021-05-05, 04:19:I got a HWINFO32 report and debug file from the system.

It looks like CPUZ messed up the SMBus SPD reading as looking in the .DBG file SPD offset 07 is 00 which is what it should be, further the SPD checksum is correct.

SMB:0:50

..... 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 0123456789ABCDEF

------------------------------------------------------------------------

0000: 80 08 04 0D 0A 02 40 00 01 75 54 00 82 08 00 01 € @ÿuTÿ‚ÿIt would not surprise me if you re-ran the CPUZ save and the value was then as it should be.

There you go.

Although not sure how this pertains to the VE 1.3.

Reply 399 of 459, by ultra_code

- Rank

- Oldbie

Another motherboard-focused question. CPU-Z (both the modern version and vintage edition) is unaware of my FIC PN-6210 dual-Pentium Pro motherboard.