gbeirn wrote on 2021-04-05, 21:08:

I am interested in the schematics since I have 20 of those PCBs already and would like to salvage them if possible.

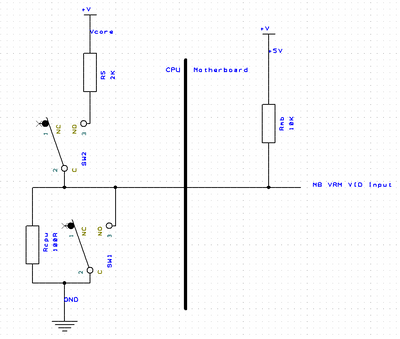

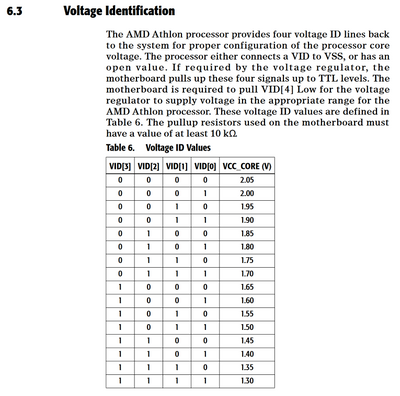

Just looking at the schematic that Wiretap posted on 2021/02/28, what value is being used for R5? It is 2k? I think that effectively means any outputs that need to be switched high are pulled up through a 2k resistor to Vcore. So if, for example, there's a VID being pulled down to GND by a 100 ohm resistor on the CPU PCB, then with a 2k pull-up to Vcore, that output will only go up to ~0.08V, so still be read by the motherboard VRM as a '0'

Similar, but not as bad, for the FID. If they're set to a '0' on the CPU PCB then they're pulled down by a 1k resistor. Which means they'll be pulled up to about 0.6V, so still be read as a '0'.

I'm going to suggest something, but be very careful. I think the idea of that resistor is to act as a current limit in case the dip switches are set wrong, with both sides 'on' at the same time. If they're both set to on, then there's a short between the top and bottom switch. Without R5 then that would short Vcore the GND. Which would be very bad for the motherboard. CPU would probably survive, although traces around the debug header might not.

But, R5 being there, and being 2k, means that the pull up is too weak to overcome the pull downs on the CPU PCB. So, and really BE CAREFUL, try putting a much lower value in for R5. As in just short it out entirely. And make absolutely sure that the dip switches are set right. Doornkaat's version has the benefit that the SPDT dip switch means it's not possible to have both sides on at the same time, so there's no risk.

Really, I think R5 should be a fuse, but it'd need to be a fast acting one. It's possible that what became R5 might have originally been a PTC fuse, but having a quick skim of some specs, the ones with low trip currents tend to have quite a high normal resistance, so might still cause problems with the pull up voltage level.

[just to add... Ah, the possibly obvious solution then is to put the fuse on the ground side instead. So have the Vcore tied directly to the top switch, then have the bottom switch connect to Gnd through a PTC, or maybe a 100 ohm resistor. Haven't thought this through yet mind.]