Reply 20 of 24, by majestyk

- Rank

- Oldbie

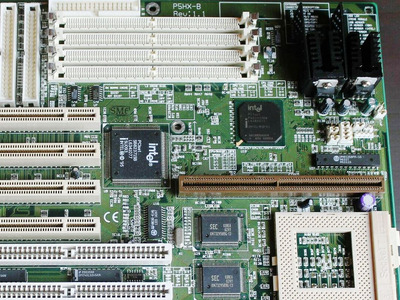

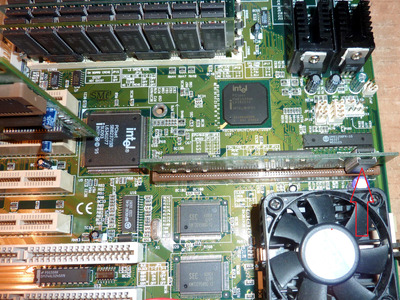

That´s a working setup. You have a total of 512K L2 Cache and the TAG-RAM soldered on the mainboard together with the one on the COAST module provides the necessary 11-bit TAG-bus width for enhanced cacheing mode.

The cachable area will be 512MB in this case.

Edit: You need to use a COAST (3.0) module with two TAG chips in this case, or, if your COAST module is a version with just one TAG-RAM you MUST populate the second DIL socket on the mainboard or your L2 cacheable area will be restricted to 64MB! (see my posts below)

If your board had 512K (= 2 x 256K chips) SRAM L2 cache onboard the TAG-RAM DIL socket would need to be populated also with a second TAG chip for the same result. In this case you don´t need a COAST module and that´s why manufacturers didn´t solder in the COAST-socket anymore in this case.

(This is because the HX Northbridge is limited to 512K L2 cache. Other chipsets like VIA can deal with larger L2 caches. Some VIA boards have 512K L2 cache onboard plus a COAST socket for another 512K. In this case there are also 2 TAG-RAMS of 32Kx8 present.)