First post, by dionb

- Rank

- l33t++

This topic is intended as a place to share information about this unusual and rather obscure board.

Description:

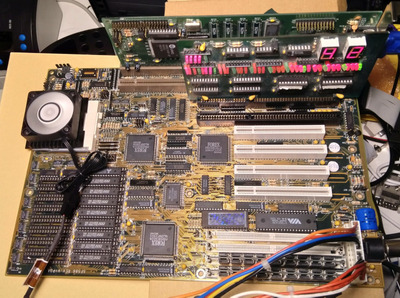

Spring Circle SF586

- BabyAT form factor

- Forex FRX58C601A/FRX58C602A/FRX58C613 chipset

- Socket 5

- 4x PCI

- 4x ISA

- 2x VLB (shared with bottom two ISA)

- DIN/AT keyboard connector

- 4x 72p SIMM slots

- 19 32p DIP sockets for L2 cache

- AT (M8+M9) power connector

- 3.6V 60mAh GP60BNKX3 NiCd barrel battery - remarkably not (yet) leaking on any of the four boards mentioned on Vogons

- no onboard I/O

Support/features:

- Pentium 75, 90 and 100 (no indication of multiplier jumper, but probably other Pentiums can work if modded on BF0 and/or BF1)

- FSB can be set to 16.7, 22, 33, 40, 50, 60, 66 and 80MHz. My board actually boots at 80MHz 😮

- max 32MB FP SIMMs supported, so max RAM = 4x 32MB = 128MB. 64MB SIMMs are recognized as 16MB.

- board can run on single SIMM, but with reduced performance.

- at least 256kB L2 cache supported with 8x 256k (32k x 8 ) SRAM chips and a 64k tag. Most likely 512kB (using 256k chips) and 1024kB (using 512k chips) also supported if suitable tag is used and we can figure out jumper settings (to-do)

- unknown cacheable limits (to-do)

- EDO *not* supported

- VLB runs at full FSB speed (unless a currently unknown jumper setting alters that), which means that it will almost always be necessary to underclock the FSB (and CPU) to get VLB cards to run, to 40MHz or below. cannot reproduce, needs more work.

- VLB appears to work at 0 WS. Older VLB cards can only support that with 33MHz or lower. Probably jumper setting to add a wait state, currently unknown (to-do)

- default turbo mode is off, which defaults to 33MHz FSB (and possibly does stuff with cache too). To enable full speed, the turbo header needs to be shorted (a jumper works fine)

Jumpers:

JP1: external battery. Looks standard, so pin 1 +3.6V and pin 4 GND. 1-2 jumpered by default (assumedly to draw power from onboard barrel)

JP2: unknown, apparently labeled "IPC 206". Default = open

JP6: unknown, probably related to BIOS. Default = closed

FSB

JP 7, 8 and 9

1-2 1-2 1-2 : 16.7MHz

1-2 1-2 3-4 : 22MHz

3-4 3-4 3-4 : 33MHz

1-2 3-4 3-4 : 40MHz

3-4 1-2 1-2 : 50MHz

1-2 3-4 1-2 : 60MHz

3-4 1-2 3-4 : 66MHz

3-4 3-4 1-2 : 80MHz *

*: overclocks board, CPU, RAM, cache, and probably VLB and PCI significantly. Use at own risk. I was not able to boot with SCSI adapter in VLB slot with this setting.

JP10/11/12/13/14: cache control. Not fully known, but some are clear:

For 256kB (8x 32k x 8 and an 8k x 8 tag), settings are:

JP10 : open

JP11 : 1-2

JP12 : closed

JP13 : open

JP14 : 1-2

For 512kB (16x 32k x 8 and a 32k x 8 tag):

JP10: open

JP11: 2-3

JP12: closed

JP13: open

JP14: 2-3

For 1024kB (16x 64k x 8 and a 32k x 8 tag):

JP10: 2-3

JP11: 2-3

JP12: closed

JP13: 2-3

JP14: 2-3

512kB with 8x 64k x 8 (and 32k x 8 tag), 1024kB with 8x 128k x 8 (and 32k x 8 tag) and 2048kB with 16x 128k x 8 (and 32k x 8 tag) should also be possible, but I haven't figured them out yet. The latter two require very rare SRAM chips, the first is just a matter of elimination (probably JP10/11 and JP13/14 not set to same setting), the second probably involves JP10 and 13 on 1-2.

JP15/16/17: most interesting block of jumpers. Probably controls VLB - but unknown for now (to-do)

Various settings seen on the boards:

JP15 2-3 JP16 2-3 JP17 1-2

or

JP15 1-2 JP16 2-3 JP17 1-2

No immediately obvious difference seen between JP15 and JP16 in 1-2 or 2-3.

Setting JP17 to 2-3 results in no boot at all, also not with crystal in OSC3

OSC3: 4-pin oscillator socket. Most likely for an independent VLB clock.

Inserting 25MHz crystal into socket does not change behaviour in combination with various settings of JP15/16/17. Still unknown how to use (to-do)

Connectors:

J7 keylock (5-pin)

J8 Turbo LED (2-pin)

J9 Speaker (4-pin)

J10 Turbo switch (2-pin) - note that this needs to be shorted/closed to run at full speed.

J11 Reset switch (2-pin)

Issues:

- Default 'auto' AT bus (=ISA) divider is anything but conservative. At 66MHz FSB, it chooses 1/4 divider, resulting in 16.5MHz ISA bus speed. This is too fast for some cards (Aztech Sound Galaxy BX II and Creatve Sound Blaster 16 CT1750 in my tests). The divider can be set at 1/2, 1/3, 1/4, 1/5, 1/6 and 1/8. At 1/8 you get a nice in-spec 8.31MHz

- Major stability issues occur with External Cache set to (default) Write-Back. Disabling this removed the problem, but affects performance.

Speculation:

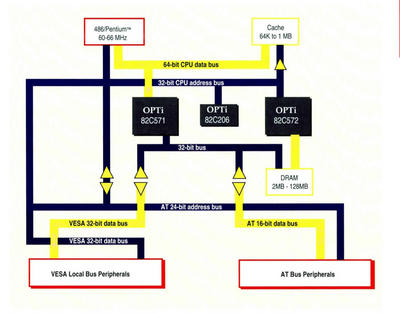

- This is the only board I can find any reference to with the Forex FRX58C601A chipset. The packages of the three chips of this chipset are exactly same shape and size as the far more widely known OPTi Premium 82C596/7 chipset. I wonder whether it isn't just a relabeled OPTi chipset...

Online resources/links:

BIOS

https://www.elhvb.com/mobokive/archive/Spring … nload.htm#Forex

(BIOS link is live as of 30/12/2020)

Forum discussions (pretty useless IMHO, but maybe someone with better Russian can dig out something I missed):

https://www.phantom.sannata.org/viewtopic.php … =18615&start=33

https://dosreloaded.de/forum/index.php?thread … men/&pageNo=369

http://www.motherboards.org/forums/viewtopic.php?t=27642

Anyway, enough for now. If anyone has more info, please share it. I'll see what more I can figure out with my two boards here and update this topicstart as and when I know more. I'll also add the info into UH19 once I have a decent amount to share.