First post, by RussD

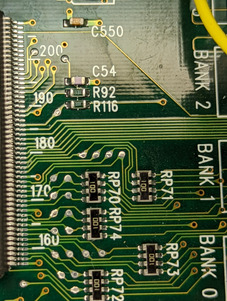

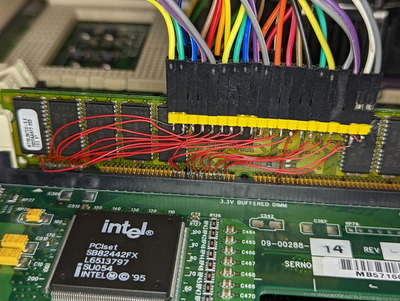

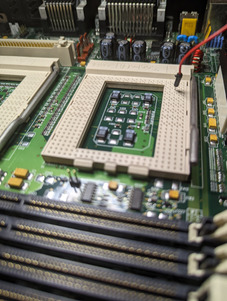

I received a Micronics W6-LI dual Pentium Pro motherboard from storage and wanted to get it up and running. I got it in a case with a power supply, video card, memory etc. And tried to boot it up. No beep, no video, nothing. Time to get down to the business of debugging the POST failure. I'll include the process I went through in this thread to debug the issue and get the board booting. And yes, the story does end with the board booting. Between waiting for tools/parts, and finding time to work on it, it took about 3 weeks. Rather than jump to the end, I'll post "updates" every couple of days or so. If people want to jump in and guess what the problem is as this goes along, you're free to do so.

Anyway, the board came with some RAM, but I had ordered 1GB of RAM since it was only $35 for the set. Pressing the power button caused it to turn on and immediately off the first time, the second time it turned on and stayed on. But no beep, no video, etc. I began by taking out all the expansion cards, swapping back in the 128MB stick that it originally had with it. Tried again. No beep. I took out the second Pentium Pro and it's VRM. Still no beep. Checked the speaker connection, tried a different speaker. No beep. Swapped the second pentium pro into the slot of the first one. No beep.

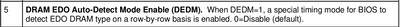

Okay, time to go a little more in depth. I grabbed a copy of the motherboard manual and verified each of the jumper settings. All correct. I next tried resetting the CMOS. No help. Checked the CMOS battery for good measure. I backed up a bit to the issue with the system initially not powering up. I left it off for a while, put all the cards back in and the second pentium pro and had the same issue again where the first time I pressed the power button, it powered on and immediately off, and the second time it powered on and stayed on. Maybe I'm dealing with a power supply issue? I don't have any others easily accessible so I put the system away for now, ordered a new EVGA 650W power supply and a cheap POST diagnostic card. Both will arrive in the next post.