rasz_pl wrote on 2022-09-17, 10:34:

Afaik VLB itself is just a small arbitration circuit added to 486 bus.

The "small arbitration circuit" is the key to implementing local bus add-on cards (like VL, or earlier local busses). A local bus cards "takes over" the frontside bus if it is addressed and stops the chipset from processing the cycle initiated by the host processor. This makes the local bus card responsible for driving the data lines on a read cycle and generating the "ready" signal to finish the cycle. Without a way to take the local bus away from the chipset, the chipset and the add-on card will be in conflict on handling the cycle.

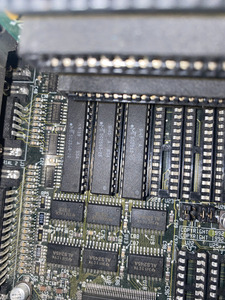

Modern 486 chipset have a dedicated input, typically called LDEV, to signal that a local bus card takes over the cycle. That pin is not on the 486 host bus, because it's an agreement between the chipset and the VL card, the host is not involved at all. Early 486 chipsets often support the 4167 coprocessor, which actually also is a local bus target. Depending on chipset design, the board decodes the C000'0000-DFFF'FFFF to the Weitek coprocessor internally (in that case, the Weitek support is of no use), while in other cases, an output pin of the Weitek processor indicating "chip selection" is used to tell the chipset that the Weitek takes over the cycle. That's exactly the same mechanism as is used for VL devices. I've got an early Opti Local Bus board that does exactly that: The LDEV pins of the 3 local bus slot and the Weitek select pin are fed into a 4-input AND (that's an OR for active low signals) gate, and the output is fed into the "weitek select" input of the chipset.

So if you want to add a VL slot to a board, and have it be connected to the FSB, you need a way to claim cycles from the chipset. You need to know how to interact with the specific chipset of the mainboard, the 486 data sheet won't help here. If there is online local bus graphics, you might be able to find the LDEV signal at the graphics chip even if you can't find a data sheet for the host chipset.