First post, by oOmDos

Hi Dear Vogons Community 😀,

I am new to this Forum, and first of all I want to thank you for maintaining this little place, i love reading topics here and today i decided to register myself as well.

I need your help and knowledge on my case. I baught a Compaq Presario 7170 and Upgraded the CPU from 90 MHZ to 120 MHZ. This was already very tricky because it was not documented how to activate the 120 MHZ CPU.

Luckily I found this post Motherboard won't run P133 at proper mhz where an undocumented PIN Selection will enable it. It works great so far.

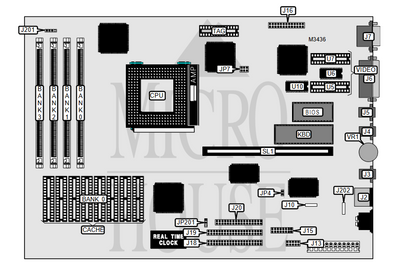

Second I wanted to add L2 Cache so I added 1x Tag and 4 SRAMs. But i have no luck enabling anything on the PhoenixBios 4.04 for the Compaq one. There is no option available in the BIOS. But there are PINS on the Board.

I did try to connect them with a simple cable, but the cache will not be available and can also noch be detected from CACHECHK or CTCM.

The Cache and Tag I Installed is: ISSI - IS61C256AH-20N

What do I need to do in Order to enable the L2 Cache on this Board?

Thank you for your support und helping me with this 😀.

You all have a nice weekend.

Kind regards