Reply 40 of 125, by rasz_pl

feipoa wrote on 2022-11-19, 01:18:Why do you say JP12 pulls down A[31:30]? It is JP13 and JP14 which either pulls A31/A30 up or down. JP12 may be irrelevent to using PB SRAM.

because you said "JP12 is also used to select between 256K and 512K". Bits[7:6] map to A[31:30]

I just saw your Jumper_block.jpg, weird that JP12 goes to tag ram, remove J13-14, keep JP15 if you cut the trace under it

feipoa wrote on 2022-11-19, 03:07:Just looked at the image of the motherboard I uploaded previously, download/file.php?id=150310&mode=view , I see traces going from TAG to the 74F245 and SRAM in parallel. Should I map them all out, or just put the 74F245 buffers back for another test?

U32 is passing A2-5 A10-11 and probably some other address lines, not what I expected. Now that I think about it I dont know what I expected 😀 but if its address bus then its one way only and they arent needed if not using 5V SRAMs

https://usermanual.wiki/Document/intel82430hx … .1819793331.pdf page 4 nice 430HX diagram with PB cache.

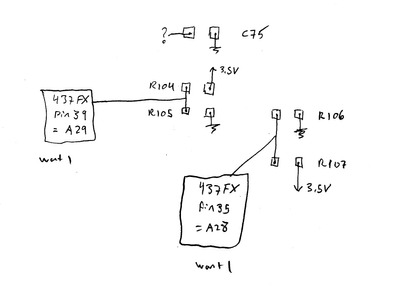

>I traced out chipset pins A29 and A30, but they only go directly to the CPU's A29 and A30. I couldn't find a jumper block where they locate.

Doesnt have to be jumper block if they didnt plan ever using those PB cache footprints, might be just a resistor somewhere and empty resistor footprint somewhere else

Imo its not possible that there is no resistor on those lines if the bios doesnt set this register, something needs to be bootstrapping A29 and A28

A29 is now (SRAM config) pulled to the ground thru a resistor, it needs to be pulled up. Look harder for that resistor 😀

are there any resistors on the back? Measure resistance of pin 39 https://www.digchip.com/datasheets/parts/data … 82437FX-pdf.php to the ground and hmm 3v supply? or CPU Vio?