First post, by mbarszcz

I have an M912 v1.7 motherboard that originally came with fake cache. This board was in rough shape when I got it, the system would barely make it past POST. Turns out that in addition to the fake cache, it had a bad voltage regulator and some questionable caps which were causing the instability. After fixing that up, and replacing the fake cache with sockets, pin headers, 512K of real cache, and a BIOS upgrade, it has really come a long way. Now it is solid as a rock and runs so much better than it did before. With L2 cache, it is so much more usable.

The board came with an Am486 DX2-80 installed, and as I mentioned, I was able to upgrade the bios to the 1995X bios. All that went surprisingly without issue.

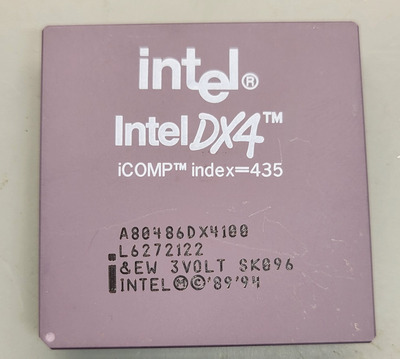

I decided to take it up another notch and upgrade the DX2-80 to an Intel DX4-100 (SK096). I set the jumpers as per the table in the manual for an Intel DX4 (see screenshot), plus the jumpers for VL Bus no wait states and to 33MHz.

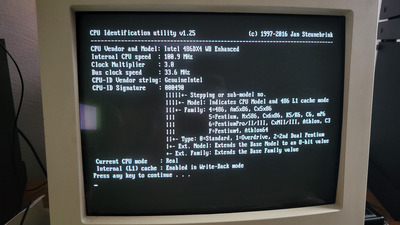

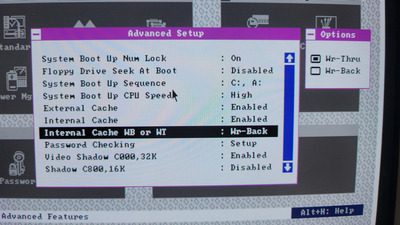

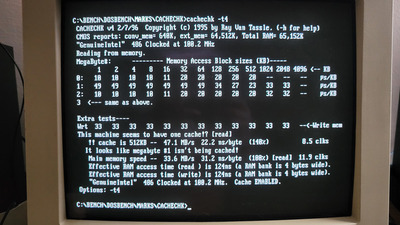

The system came up, and I set timings set to 2-1-1-1 with no ram or cache wait states, and everything seemed to be working solid in write-thru mode. When I enabled L1 write-back in the bios options, things started to get goofy. cachechk reported that the first 1MB wasn't cached, cachechk in write mode showed steady performance across the block sizes (indicating effectively write-thru mode), chkcpu still showed write-through mode, and the quake and chris's 3d benchmark ran very poorly. After resetting it back to write-thru mode, everything seems back to normal.

So with that in mind, it seems that the CPU/board run fine in write-thru, but for some reason, write-back isn't properly supported and starts causing strange behavior.

Since the CPU was a China ebay special, I took the CPU out and gave it a good scrub with some acetone to make sure it wasn't relabeled, and it certainly looks legit, no signs of re-markings. The label is engraved in the CPU, not just screen printed on. This thread seemed similar to my situation, but in the end it turns out the guy had a fake CPU PC Chips M912 BIOS update for Am5x86 and Cyrix 5x86

With the chip saying &EW on it and cpu-world.com saying that the chip supports write-back https://www.cpu-world.com/sspec/SK/SK096.html, it certainly seems that this setup should be capable of write-back mode.

Other things I've tried with no success:

- Fiddling with the undocumented jumper JP36 (that just causes the L2 cache to be detected as 32K but not work)

- Using the Award BIOS instead of the AMI BIOS

- Modifying the Award Bios to force write-back mode (this didn't work and still came up as a grayed out as the grayed out write-thru option. It's like the board doesn't know what to do when write-back mode is forced on it.

Does anyone have an M912 1.7 working in write-back mode successfully, even better with a DX4-100? Any ideas what I might be missing?