I ran out of things to route based on placement of tracks on pcb. What is left is logical deduction. Looking at the diagram there are some things that confuse me.

I understand R1 R2 limiting TAG ram addressability with smaller cache.

I somewhat understand R5 R6 linking last cache address bit to second bank thus switching from 2 bank arrangement to single.

What I dont understand is what is happening with R3 R4. What would be the point of cutting off CPU_A13? Wouldnt unpopulated R3 leave uncached holes? or worse broken cache every 16KB as cache not seeing CPU_A13 couldnt distinguish real addresses? ... wait a minute, its not CPU_A13!! 😁 looking few posts earlier

>>A13

>>A16

>the only two swapped address lines!

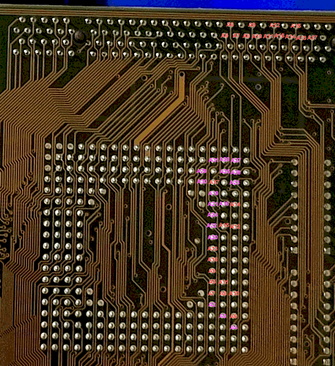

FIC didnt swap those after all! RockstarRunner how could you? top 10 anime betrayals! :] A13 is Q-10, A16 Q-9, after swapping A13 A16 back R3 R4 makes perfect sense, I think this is allowing using much cheaper 8KB chips. This made me look at your picture more closely, there is in fact bottom layer track between CPU A4 and cache slot a22 just like I guessed there would be in the diagram called under_U1_1 😀 lovely, so address bus is 100% correct.

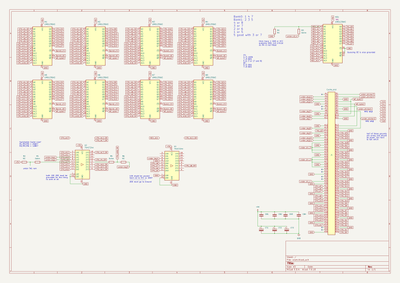

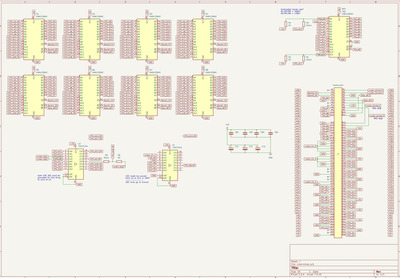

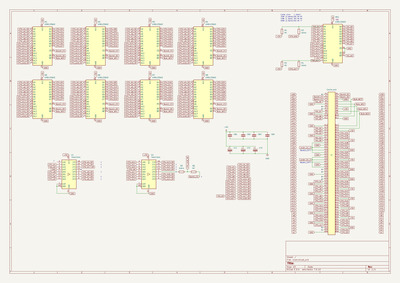

I think this is the final resistor function description (not 100%, still needs validating):

Cache size:___________| Populate 0ohm:

256K (2 banks, 8x32KB)| R1 R3 R5

128K (1 bank, 4x32KB) | R2 R3 R6

64KB (2 banks, 8x8KB) | R2 R4

I wonder what the real world difference there is between those three, especially between 4x32KB vs 8x8KB. Hope RockstarRunner tests it if we manage to finish this project successfully.

Im tapped out at the moment. Attaching progress. 0 errors, 7 Warnings. 5 connections missing, 11 guesses and assumptions on U1 U2 and some more on common lines.

Majestyk could you please check some things for me?

- U1 2? I have no idea where it could be connected to

- U1 3 to M1 5?

- U1 7 to M1 7?

- U1 9 to M1 8?

- U1 14 to M1 26? is it connected to VIA right above U1?

- U1 16 to M1 9?

- are all M1-M8 pin 10s connected together? This doesnt make sense logically, I have a feeling it should be split into groups M1-M4 and M5-M8.

- U1 18 to M1 10 or M5 10?

- U2 12 to m1 4? is it connected to VIA right above U2?

- U2 14 to M1 3?

- U2 16 to M1 25?

-cache slot a28 a30-a32 to a56 or a57? I wonder why so many connections bundled together

-cache slot a34-a36 a38 to a57 or a56? I wonder why so many connections bundled together

-cache slot a56 to M8 20?

-cache slot a57 to M4 20?

-cache slot b57 to M8 22?

-cache slot b58 to M3 22?

-cache slot b55 to M8 M4 27?

-cache slot b54 to M7 M3 27?

-cache slot b53 to M6 M2 27?

-cache slot b51 to M5 M1 27?

I thinks thats all, this might be the final stretch.