Baoran wrote on 2023-07-12, 12:59:

How does this apply with 2 motherboards having exactly same symptoms including system freezing when trying to slow down the system using turbo button when in WB more? Especially when one of them is PCI motherboard and the other one is VLB motherboard? The LS-486E PCI motherboard was made in 1996 which is way after that cpu was released. I could understand this if the problem was only with the vlb board that has made before the cpu was released.

Hi Baoran,

I don’t have a ready explanation about the LS-486E Rev D board, the Am5x86 in L1 cache Write-Back mode should just work.

But the problem with the DataExpert EXP4045 is most probably a BIOS issue! What does the BIOS display as CPU type when you run the Am5x86 in x4 multiplier mode?

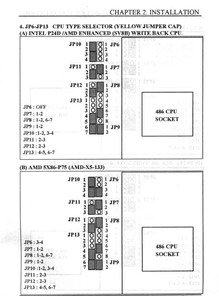

In addition to the excellent replies from @Deunan, explaining the need of connecting 2 or 3 extra signal lines between the CPU and chipset to get L1 WB working, the BIOS plays a role here too. The BIOS, when detecting a WB capable CPU and this CPU is jumpered for WB mode, must program the chipset registers for the L1 cache WB protocol and enable the extra signal lines.

Failing to do so will result in the WB problems you described.

On the EXP4045 board, you can test the correct functioning of this L1 WB CPU/chipset/BIOS dance by setting the Am5x86 in x3 multiplier mode. In this mode, the Am5x86 will behave exactly like an Enhanced Am486DX4 CPU including its CPUID and L1 WB mode support.

Because your July 1995 BIOS supports this Enhanced Am486DX4 CPU, it should report this CPU on the boot screens and let the Am5x86 work correctly in x3 multiplier and L1 WB mode.

If this works fine now (try booting from a bootable floppy as ultimate test) you know the jumpers are set correctly and the Am5x86 is good. But you need a BIOS update. 😉

Can you post a dump of the EXP4045 v2.3 BIOS here so I can help you with an update?

Greetings, Jan

Edit: Did you see my old Am5x86 article about getting this CPU running on most socket 3 boards? It is still available on my website:

http://www.steunebrink.info/amd5x86.htm