tauro wrote on 2023-09-18, 23:22:

On a 486:

The CPU has cache memory called L1 (level 1). It can be 8KB or 16KB depending on your CPU. Earlier ones have 8KB, later ones 16KB.

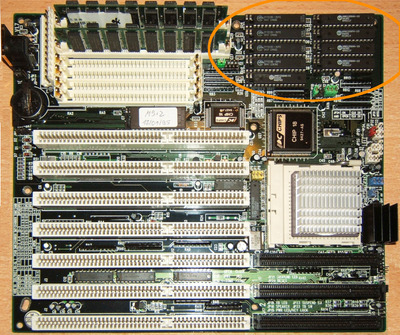

The motherboard may or may not have cache memory, called L2.

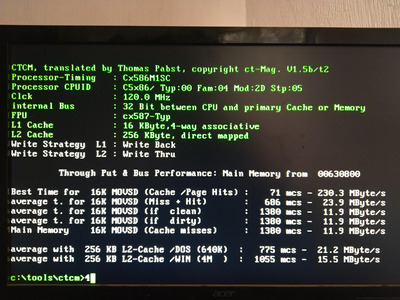

Cyrix 5x86 have 16K.

tauro wrote on 2023-09-18, 23:22:

According to the link you posted, your motherboard does not have L2 cache. So you don't have to worry about that.

Sorry for that, there is more than one model of A1GX-2, see : https://theretroweb.com/motherboards/s/acer-a1gx-2-w-cache

For the rest of the jumpers, it's the same

I have 256K

tauro wrote on 2023-09-18, 23:22:

And you don't really have to worry about L2 cache for a 486. Upgrading the CPU is far more important if you want a faster 486, the BUS speed and waitstates are also very important.

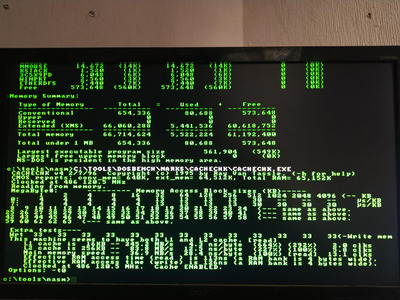

All benchs went off the chart since I have upgraded the ram and set the L2 to 0WS/0WS. Ram upgrade alone change nothing in the benchs except for 7-zip (7za b)

For now, only 48MB of ram (16MB not cached), instead of 32MB (fully cached)

As for the CPU, it's a Cyrix 5x86 @ 120Mhz, with the experimental stuff on (the safe one, no BTB).

The not the fastest 486 but it's not far.

tauro wrote on 2023-09-18, 23:22:

Disk drive caching is a different subject.

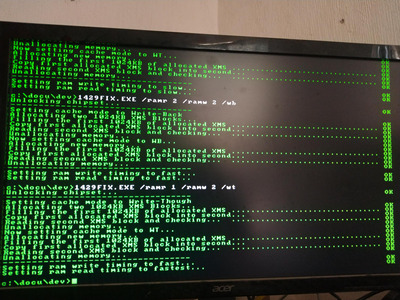

Indeed, the backup idea (if even possible) was to use the extra ram for disk caching if possible, Keep the cached RAM for the programs and the uncached RAM (anything over 32M) for the disk cache (Still faster than CF in PIO3...)

My actual limit, is the motherboard... You know, very limited ACER BIOS.

And onboard cirrus logic video card, It's "VLB" but well, it bench between ISA and VLB, it's really under-performing, and there is no actual VLB slot.

Would also be cool to know why the PC crash with the L2 to 0ws/0ws instead of 1ws/0ws if I run the jumper configuration in Cyrix 5x86 config, but it work just fine with a nice performance uplift if a set the board jumper to "Intel 486"