First post, by TheMobRules

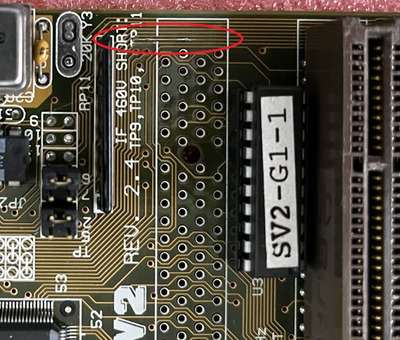

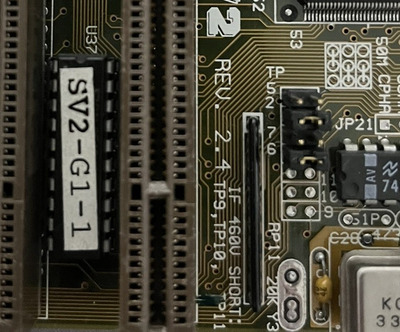

EDIT: read the post below, the problem was due to a broken trace.

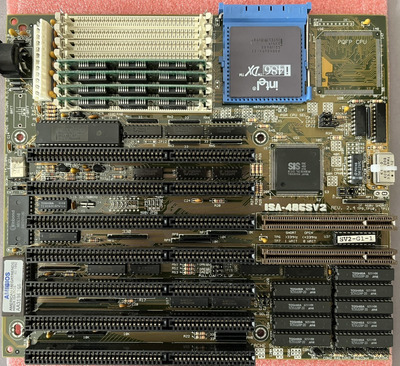

I've been restoring an ASUS ISA-486SV2 rev 2.4 motherboard, I got it very cheap as it was listed in "not working" condition and was also full of grime, most of the SIMM slots were mangled and broken (as if someone had just ripped out the modules instead of unlocking the clips), leaking battery had been removed by the previous owner but there was some corrosion near ground zero.

I first cleaned the corrosion, removed socketed components and gave the board a good wash with deionized water. Then, I proceeded with the repairs: re-tinning dull solder around the battery area, replaced a couple of 47pF ceramic caps that had been obliterated by the corrosion and replaced all SIMM slots with new ones since the original ones were unusable. The board ended up looking pretty nice, very shiny and without need for bodge wires or other unsightly fixes:

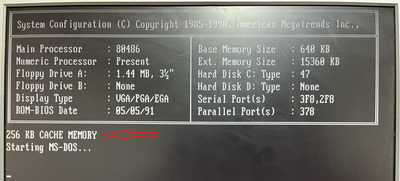

The first few tests were promising, as it booted right away, was able to enter the BIOS, configure the settings and all that. The problems started when trying to boot DOS, either from a floppy disk or a hard drive, as I always get a longer than usual "beep" after POST followed by a "0KB CACHE MEMORY" message before the OS tries to boot and hangs at "Starting MS-DOS...", even if I set L2 cache to "Disabled" in the BIOS.

However, I have noticed that if I remove the cache TAG chip I can boot to DOS with L2 cache disabled and everything works as expected other than the obvious penalty performance of not having L2 cache.

I'm not sure how to proceed with the troubleshooting at this point, so I will list all the symptoms I am experiencing and things I've tried so far in case someone has an idea of what may be happening here.

This is what I've found during my tests:

- As mentioned above, regardless of the cache configuration I select with the jumpers and SRAM chips, I always get "0KB CACHE MEMORY" after POST

- The OS will NOT boot (even with L2 disabled) unless I remove the cache TAG chip, removing it boots and works properly but obviously with L2 disabled in the BIOS

- When the TAG chip is inserted, I get a slightly longer "beeeep" after POST as opposed to the regular "beep" and correct behavior when the TAG is removed

- I tested with several sets of working SRAM chips (in both 128KB and 256KB configurations) and got the same results and the "0KB CACHE MEMORY" message

- The set of Toshiba SRAM chips that came on the board test OK in my TL866 and appear to work just fine on other motherboards

- No chip gets above barely warm, the "hottest" one is the 74F245 near the SRAM chips, which may be suspicious due to its location but it doesn't really get hot, just warm

- Tested with various CPUs, memory modules and ISA/VLB graphics/controller cards, all of them seem to work and have no effect on the L2 behavior

- There is some oxidation on the 14.318MHz crystal due to the battery leak, but not sure if this has anything to do with the cache, especially considering the board works fine without L2

Any help or suggestion is appreciated, right now I'm leaning towards something being wrong with the cache selection jumpers and the associated decoding logic, but I need to understand how the circuit works first. I am attaching the manual for this board I found in the Retro Web as well as a BIOS dump (it seems like an older version than the one available at the Retro Web).