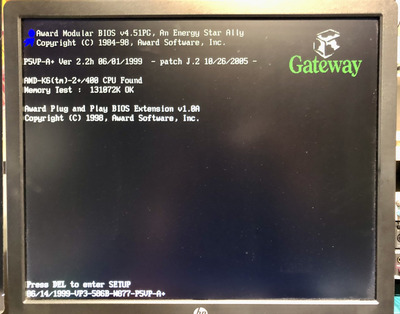

My VisionTop S7-MVP3 (rev. G) has 2.0V so I was able to put the K6-2+ directly in it without the interposer, which freed it up to use on my socket 5 machine (now it's a Pentium MMX 233 instead of a MMX Overdrive 200). I took a chance and flashed an extra 128K EEPROM with the mod from Jan Steunebrink's repository (which doesn't specify what revision his bios is for). IT WORKS FINE on the REV G!! It's not as full featured because it's only 128K instead of the 256K rom on my ECS P5VP-A+ --- but it works at 83MHz fsb!

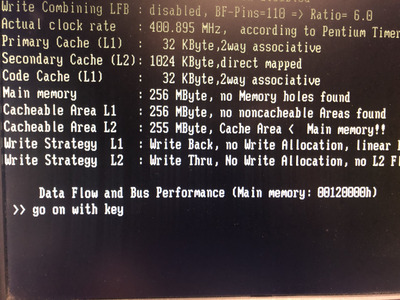

I settled on 192MB of memory (3x64) mostly because that's what I had other than the single 256MB stick. I tried 2x128MB but the system only detected one of the sticks. So I'm just gonna go with 192MB for now and see how that works out. I think 98SE would run slightly better with the full 256MB -- but at least I get an extra 100MHz this way!

I might attempt to replace the cache chips on the ECS board one day -- but for now it's in the questionable pile.

Thanks all,

Evan