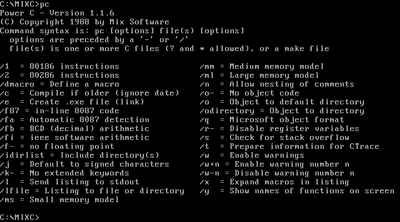

Those switches for 186 and 286 are just for the support of different instruction sets. I.e. a 186 has a more evolved instruction set over an 86, and a 286 has a more evolved instruction over and 286, and a 386 is 32bit instead of the prior 16bit processors.

When a C compiler generates the byte code, then that byte code targets a specific processor instruction set. I.e. byte code for a 286 using instructions specific for a 286 will probably be more efficient than byte generated for a 186 just using the instruction set of a 186. This is why the x86 family of processors are backward compatible. I.e. a 286 can execute everything that a 186 can execute. But not the other way around.

Memory models don't allow to allocate more than 64kb in real mode. It simply allows your compiler to create an abstraction layer for addressing memory. I.e. give you the illusion that you can allocate larger blocks at a performance penalty. Behind the scenes, the compiler has put in place a mechanism that spans multiple 64kb blocks, giving you the illusion it's one big block of data.

More on memory models: https://en.wikipedia.org/wiki/Intel_Memory_Model