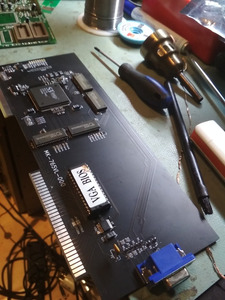

Trio64V+ and Virge use same pinout. This is interessing point. Trio64V+ and ViRGE is very fast in DOS-mode. No difference, if ROM is same.

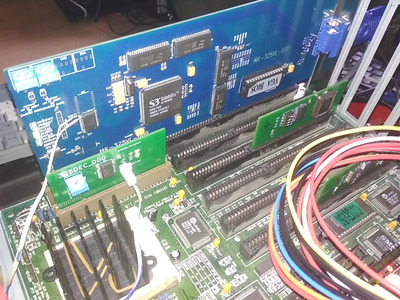

But i am now on one point: STB Powergraph 64VL is not capable to swapping to ViRGE. Dito my first draw with configable address decoder.

S3d-game need linear framebuffer up to 4MB. And it is freezed with first ViRGE_VL draft.

Same result with useage of linear framebuffer on Trio64V+ VLB and S3VBE20. S3VBE20 tell me, linear framebuffer at 64MB. It is not correct. (128, 256, 384MB address, mirrored )

After start of s3d-game is address-range above 64MB and it is freezed. Alright, i am one step forwards. 😀

My solution with address range is same with proposal from MrKracher.

0xA000-0xBFFFF -> SAUP1 (memory , use for old mmio)

free config address -> SAUP1 (memory)

free config address +16M Offset -> SAUP2 (register)

modified Trio64V+ ROM tell: it is 64MB offset . -> config to 64MB Address (or i change value of ROM to 128 or 256MB offset )

Address schema is same with PCI address space. (0-4MB linear framebuffer, 16MB register, above 32MB is for Motola system ( big-endian ) )

Now, i am waiting on this second PCB (only address decoder for plug into seconds VLB slot and it is connecting to frist PCB draw. )

if it is a success -> huge modification from frist draw is neccessary.

Modification:

Trio/ViRGE is not ROM-decoder anymore, it got own address decoder on ISA BUS. (already checked )

4x address-decoder and LVC-gatter instead old solution with 74F260 for Trio64V+ and/or configable single address decoder.

Greetings

Matt