First post, by GloriousCow

- Rank

- Member

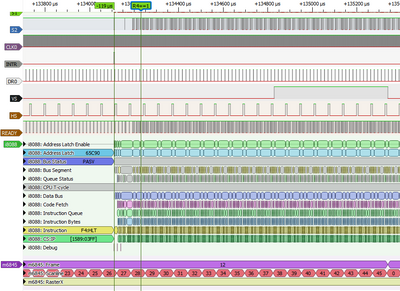

In my course of investigating my bus capture of Area 5150's "Lake" end credits effect, I discovered something interesting.

The effect goes through a chain of interrupts that set up a vsync interrupt that triggers each frame of the effect. The purpose of the chain is to position the interrupt at a specific point on screen that isn't strictly at display enable or some other easily pollable location. I've noticed that despite my best efforts I seem to have a bit of inaccuracy with where MartyPC comes out of the interrupt chain vs where hardware does.

The bus sniffer shows something quite interesting:

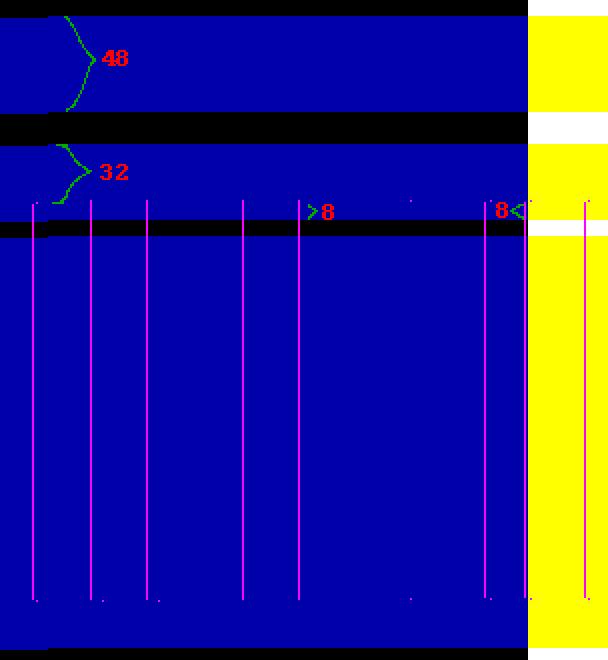

On the Motorola 6845 CRTC a vsync is always 16 scanlines tall. That's sort of taken for gospel; the Amstrad CPC compendium just states it several times. And yet, here we have an 8 scanline vsync.

This is taken right off the CRTC's VS pin, so we're not dealing with any of IBM's shenanigans.

Moreover, there's no indication on the CRTC that a vsync should be appearing here. Looks like a case of phantom vsync.

VileR put together a nice article on the subject here: https://int10h.org/blog/2023/03/cga-6845-crtc … m-vsync-glitch/

there's just one problem - vsyncs, phantom or not, are always 16 scanlines, tall, aren't they?

I went back to VileR's capture of Area 5150 on youtube, and by some miracle, wouldnt you know, at 8:26 ...

there she be. this 'impossible vsync' is, unfortunately included in Area 5150's effect interrupt setup timings. Talk about breaking your emulators...

MartyPC: A cycle-accurate IBM PC/XT emulator | https://github.com/dbalsom/martypc