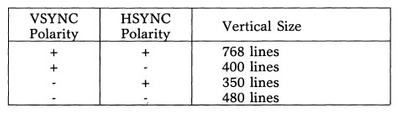

Grzyb wrote on 2024-01-28, 14:19:SYNC polarity tells the monitor which mode it's supposed to switch to:

sync.jpg

That's the original IBM VGA and 8514 standard. […]

Show full quote

SYNC polarity tells the monitor which mode it's supposed to switch to:

sync.jpg

That's the original IBM VGA and 8514 standard.

Later on, non-IBM SVGA appeared, with the 800 x 600 resolution.

Of course, it wasn't possible to select the 600-line mode using SYNC polarity alone, and monitors had to use additional methods.

Won't the HSYNC polarity being negative clash with detecting HSYNC itself? Since it needs to go high every hsync period to properly cause flyback of the beam?

I'd guess VSYNC polarity can still be detected from observing it change into it's intended value when HSYNC goes high (from 0V to 5V or whatever, when it starts), but won't negative HSYNC polarity (it lowering during HSYNC) cause issues detecting HSYNC? How does the monitor detect if it's to retrace (activating the coils) when it goes high or low if it's diffent in different polarity modes?

Afaik on an EGA, the VSYNC polarity also determines the pins used during active display (to select EGA or CGA mode in the monitor (mode 1 vs mode 2 it's called I think)? Then what effect does HSYNC have there (on a EGA monitor)? Or will the monitor simply fail in that case (since HSYNC is behaving inverted, it's no longer valid)? Or is the signal actually 3 states (positive,negative,inactive)?

If the idle and active states are swapped, won't the signal be unreliable because the active driving or non-driving states are essentially useless (no way to determine if it's driving (retracing) or idle(normal display))?

Say you say it's positively decoded:

1(5V)=retracing now

0(0V)=not retracing

All's fine in that case, since the retracing can be driven directly from that (only some simple transformation to higher voltage).

Then if you'd reverse that (negative sync):

0(0V)=retracing

1(5V)=not retracing

Now you'd have the issue of not being able to differentiate and seperating the two cases, as 0V both means to drive the coils(0V=retracing if negative sync) and not retracing(0V=not retracing, if positively sync).

The same issue with the voltage swapped (but reversed).

So there's no way to tell if the VGA wants to retrace or not, as the signal would (looking it at it from a binary on/off state) become unreliable to tell one from the other (sync vs non-sync states are both defined to be the same)?

Also, unless the HSYNC's driving (retracing) state if dormant, you can't count lines (so can't reliable detect VSYNC based on the length of a VSYNC pulse), thus even VSYNC's positive/negative information is useless? Or does it simply count the lines by detecting raw state changes (high-low-high as well as low-high-low)?