First post, by GloriousCow

- Rank

- Member

I'm confused about the SOM field in the End Horizontal Retrace Register.

Ferraro has this to say about it:

Determines whether an odd or even memory address should be used as the first memory address after a horizontal refresh

=0 Start at an even memory address

=1 Start at an odd memory address

IBM's document says:

Start Odd/Even Memory Address-This bit controls whether the first CRT memory address output after a horizontal retrace begins wi […]

Start Odd/Even Memory Address-This bit

controls whether the first CRT memory address

output after a horizontal retrace begins with an

even or an odd address. A logical 0 selects even

addresses; a logicall selects odd addresses. This

bit is used for horizontal pel panning applications.

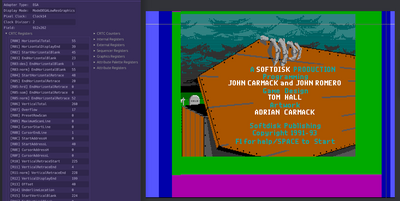

Both of these descriptions are a bit ambiguous. Take for example, Dangerous Dave in the Haunted Mansion.

Dave's title screen starts out with a CRTC start address of 0.

The screen then pans to the right, incrementing the start address to 40, one byte at a time.

However, the scrolling as i have implemented it is very jerky. I would expect a sequence of (start address, pel panning) updates to be (0,4)(1,0)(1,4)(2,0)(2,4) and so on, to effect a smooth pan.

Instead i'm seeing: (1, 0)(2, 4)(3, 4)(4, 0) ... it doesn't make much sense.

I was wondering if somehow the SOM bit is affecting the memory start location. If SOM==0, then we should start each scanline on an even address - so what effect does that have when the crtc start address itself is odd, like ==1?

We know that pel panning is not latched - it can be updated per scanline (as demonstrated by Beverly Hills Cop's wiggly text effect)

I saw mention of preset row scan being used for scrolling operations, but in this effect it is set to 0 and never updated.

There's also nothing going on with display enable skew or horizontal retrace delay.

What is the secret i'm missing to smooth scrolling?

MartyPC: A cycle-accurate IBM PC/XT emulator | https://github.com/dbalsom/martypc