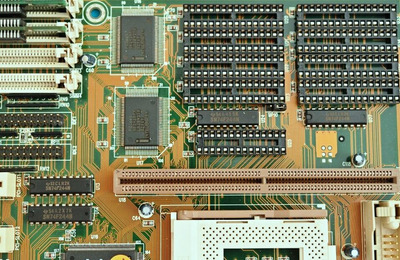

majestyk is right: These chips are not 32-bit async cache chips, as I claimed, but they are part of the three-chip north bridge. The north bridge on the 430FX chipset consists of one 82437FX chip that contains all the control logic and deals with addressing, whereas the data itself is routed through the two 82438FX chips. These chips connect to 32 data bits of the processor, 32 data bits of the RAM and 8 data bits for the PCI host interface each. Both chips combined result in a 64bit/66MHz interface to the processor, a 64-bit interface to the RAM and a 16bit/66MHz interface to the PCI host logic. The PCI host logic then obviously translates this to 32bit/33MHz. These chips are not involved when accessing the L2 cache: The data lines of the L2 cache are directly connected to the frontside bus, so transfers between the Pentium Processor and the L2 cache are performed by the 82437FX without assistance from the 83438FX chips.

In the datasheet, the 82437FX is called "System Controller" which is abbreviated as "TSC", whereas the 82438FX is called "Data Path" which is abbreviated as "TDP". The letter "T" is not explained, but it might be related to the code name "Triton" of the 430FX chipset. The reason the north bridge is split into three chips is that the 430FX uses QFP chips. The 82437FX is in the biggest QFP package available, it has 208 pins. This is just not enough pins to deal with a 64-bit FSB that is decoupled from a 64-bit memory data bus (this requires 128 pins, which is more than half of the pin count of a QFP208), so the north bridge function had to be split into multiple chips. The 430HX approached this challenge in a different way: The north bridge of that chipset is a BGA chip.