Tetrium wrote:

It might have just been a marketing thing or perhaps a way to have fewer RMA returns (I'm just guessing though)?

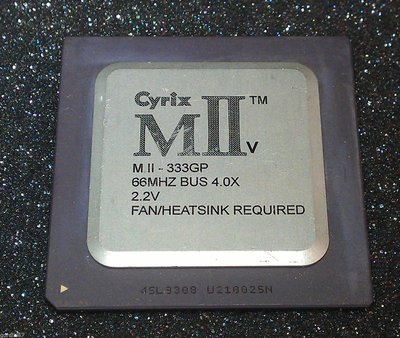

The 2.2v parts often have the 100MHz FSB and the older 2.9v ones have official FSB settings that are around the max that non-super7 boards can provide.

The vast majority of MII 366 (2.5x100) chips seem to the te 250 nm 2.9V model while the 95x3 PR400 seems to be the most common 2.2V part. (with a smattering of 250 and 266 MHz 2.2V parts of varying bus speeds -though mostly 100 and 66 MHz from what I've seen pop up on ebay)

The lack of 266 MHz (4x66) 2.9V parts seems more likely to be multiplier limited (of the 250 nm core) where the 180 nm refresh added 4x and higher multipliers.

Still, it seems a bit odd that it took them so long to put out the 2.5x100 MHz model given they put out so many 83 MHz rated parts. (or a 2x100 MHz model soon after the release of the 3x66 and 2.5x83 MHz parts)

This means people who wanted a faster chip which had a maximum voltage setting that the older boards (officially) didn't provide, would be more guided towards getting a slower chip with higher voltage from Cyrix so there would be fewer returns of the 2.2v parts which would have quite a bit of difficulty working at 2.9v or 2.8 volt which often was the minimum voltage available officially.

I think they just pushed the voltage as high as the chips could reliably handle (without damaging the circuits our producing unreasonable amounts of heat -though they never pushed into the 30+ watts range like the 3.2V K6-233). Compatibility with older boards was a plus, but like the Winchip, I think it was more of a yield management system. (same for the K6's 3.2V and K6-2's 2.2 and 2.4V when Intel stuck with 2.0V -or the K6-2+'s 2.0V rating to the 1.75V Athlon and 1.65V Duron and Coppermine parts)

Cyrix also pushed their 180nm parts to the reasonable edge of voltage tolerance at 2.2V when overclockers (and boards supporting such) limited things to 2.0V. (and the K6-2+/III+ strictly limited max voltage to 2.0V in documentation -though realistically you /could/ run them at 2.2V without risking damage at the circuit level -just need to cool them a bit better) Cyrix did also use 2.2V rating for some select 250 nm parts, but this was for their embedded/mobile low-power CPUs.

I'm honestly a bit surprised they never went above 2.9V during their 350 nm process usage like AMD did with the K6. (might have been able to push out the 200-233 MHz 6x86MX sooner ... or prior to that, might have been able to push the older 6x86L to 3x66 MHz running above its standard 2.8V -on that note, my 6x86L PR-200 actually runs stable at 3x66 at 3.2V ... maybe a bit lower than that even, I didn't exhausitively test minimal voltage required, but I know the 350 nm process used tolerates up to 3.5V -or a bit more even- provided there's reasonable cooling)

Plus, if Cyrix wanted to maximize compatibility, they'd have gone with 2.8V and not 2.9V given the Pentium MMX and 6x86L standardized at that voltage. (the K6-166 and 200 opted for 2.9V for yield reasons like Cyrix had)

As an asside, a good number of non-super 7 boards that lack proper 2.2/2.4V support at least have a 2.5V setting, sometimes undocumented sometimes not. And indeed, there were press releases for Cyrix that promoted the 6x86MX at 2.5V on a 250 nm process, though this never related to official parts.

And as far as not pushing 3.5x83 or 3x100 MHz 2.9V parts (given a good number of 233-250 MHz parts do seem to run stable at those settings), your argument for older motherboard compatibiltiy might be significant as far as voltage regulators coping with the power use. (albeit any board that struggled with a 300 MHz 2.9V part would probably have had problems with the 3.2 or 3.3V K6-233) Additionally, I will agree that sticking with 2.9V consistently (at least up until it was dangerous to use -like with 180 nm parts) was probably for ease of consumer installation and motherboard matching on top of their own yields. (given both my 2.9V parts run fine at their rated speeds when knocked down to 2.2V -though they don't overclock well if undervolted, unsurprisingly)

After NS took over management, the change in business strategy also probably put a damper on innovating higher performance market segments (the MII seemed to be relegated to supplemental income in the budget range with more emphasis put into embedded system-on-a-chip design -and plans to re-spin the SoC core into S7/S370 as somewhat of an afterthought). That might be the reason the 100 MHz FSB parts arrived late, and certainly a likely reason Cyrix stopped pushing for even higher bus speeds (like pushing for officially rated 112 MHz FSP MVP3 boards or even 124 MHz -which pushed the PCI bus to 41 MHz like early 83 MHz bus boards did -or all 83 MHz TX boards; the 105/110/115/120 MHz offered on some Ali based SS7 boards would be less interesting given they were poorly matched to Cyrix parts ... that is HAD Cyrix stayed on target with their 1996/97 market model in '99)

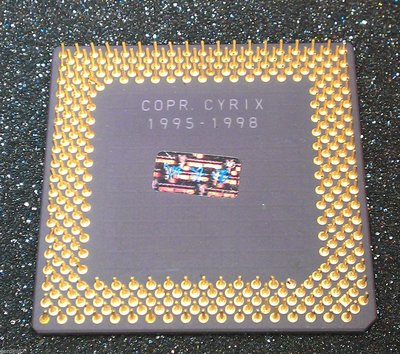

And I previously made a mistake referring to my PR366 as an IBM part, I rechecked the serial number and it was indeed a National Semiconductor 250 nm process chip. (runs fine at 3x100 MHz 2.9V so long as it doesn't overheat, but 2.5x100 MHz at 2.2V can run fine with passive cooling, at least at normal ~70F/24C room temps)

There are K6-2 parts which were only rated at 66MHz FSB, but such chips were very uncommon, so it could be it wasn't much of a problem, and afaik it was very uncommon for overclockers to not be able to significantly overclock a chip unless they significantly reduced the FSB, even though the rest of the hardware would have no issue at that speed (so it was absolutely certain that only the CPU itself made overclocking the FSB next to impossible).

It was mostly early K6-2 parts that were 66 MHz rated (the 266 and some variants of the 300) aside from mobile parts that tended to stick with 66 MHz fsb more often. AMD avoided any of the clock speeds that pushed the PCI/AGP bus out of spec, hence no 75 or 83 MHz parts or ones pushing beyond 100 MHz. (at least not officially speced as such) Plus by the time SS7 boards with 2.5x PCI dividers showed up (for 33MHzPCI/83MHz FSB) arrived, they all had 100 MHz support anyway (with a few possible exceptions like some VP3 based boards) and aiming at 100 and 95 MHz made more sense.

Given AMD's willingness to push 2.4V parts (and 3.2V on the K6-233) I'd bet they would have pushed K6-2 and K6-III parts higher for yield reasons (so-called factory overclocks) if not for heat generation becoming unreasonable and SS7 motherboards being poorly suited to fitting large heatsinks. (plus scaling back K6-III production in general due to Athlon demand and the fact the normal K6-2 didn't gain much beyond 500 MHz ... and they had something better -the Athlon- for the high-end and didn't need to push the K6-2 or 3 that hard) Plus, given motherboard stability and real-world performance, offering 110 or 112 MHz bus rated K6-2's would've been more significant.

I'm a tad more surprised Intel never resorted to overvolting their parts, particularly in the Coppermine days when they fell behind the Athlon in peak performance and raw clock rate. And their awkwardness with the PIII 1133. (pushing it up to 1.8V or 1.9V probably would've solved the stability problems -and given overclocking experience, and electrical limits of the CPUs, going up to 2.0V and 1.2+ GHz would've been realistic) It's not like Athlons weren't pulling out more wattage than those existing PIIIs ... and even at 2.0V a coppermine PIII wouldn't start to pull out ahead in heat/power of the top rated Thunderbirds until you got close to 1.4 GHz. Then again, it's also slightly odd they never released an 8x133 MHz (1066) PIII just to have something stable above the 1000 MHz part.

On a more general Cyrix history note, I was browsing around some articles (some I'd read before but missed details on) and noticed a bit more on the 6x86's FPU, particularly that the FIFO queue is 4-instructions deep with a 4-deep store queue as well (I assume that'd be 4x64-bit words for buffering FP data ... or maybe 80-bit) so more than the single-op FIFO buffer I'd assumed.

http://www.alaska.net/~akusedpc/pages/cyrix/6x-tb.htm

http://www.azillionmonkeys.com/qed/cpuwar.html

Both those mention it and the latter addresses the more general speed issues of the FPU which I was well aware of. Lacking of pipelining and ability to parallel execute FP and Integer operations isn't a major bottleneck on the 6x86 or MII (or Cyrix 5x86) and neither are the Fdiv and Fsqrt instructions, but just the common Fadd, Fsub, Fmul, and Fxch operations (all 4 cycles at peak throughput, some with latencies of 6-7 cycles vs the P5 and P6 FPUs having 1-2 clock throughput and 3-4 clock latency for all of those ops. (some have effective 0 clock execution for superscalar execution -like Fxch) So the 6x86 wouldn't have benefitted from including a PIPELINED FPU as some articles and critics claim, but just needed faster operation on those common functions.

The K6 and K6-2 are much faster on all those operations and have lower latency than the P5 or P6 (all 2-clock throughput and latency, except the later CXT core K6-2 that has superscaler -0 clock execution) but from all I've managed to dig up, is a single-stage execution design without added FIFO queue or similar buffering (let alone formal execution pipeline) to facilitate overlapping ALU and FPU operations. The K6 seems to take more of a hit from P5 or P6 optimized FPU scheduling than the 6x86 does, or rather the 6x86 doesn't seem very dependent on FPU scheduling in general due to the FIFO and generally slow execution. (the K6 would probably benefit more from a FIFO buffer than the 6x86 does, given the latter needs a pretty high portion of integer code interleaved with FPU calls to balance parallel execution while the K6 would fit in much more with 1:1-ish integer/FPU execution timing parallelism that the P6 and P5 benefit from)