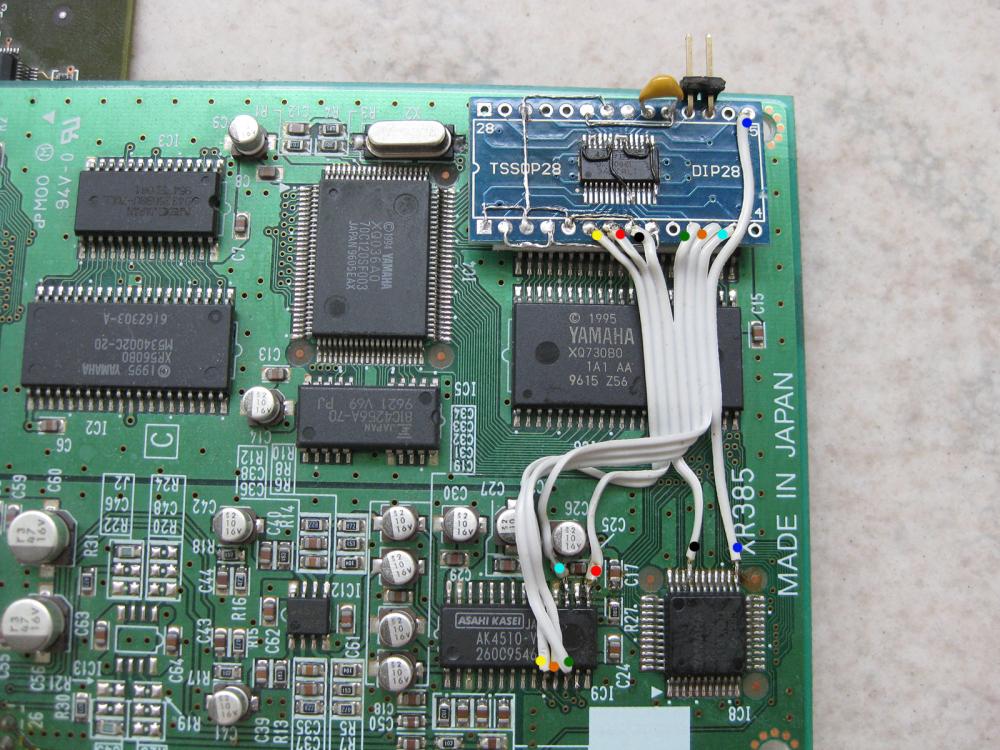

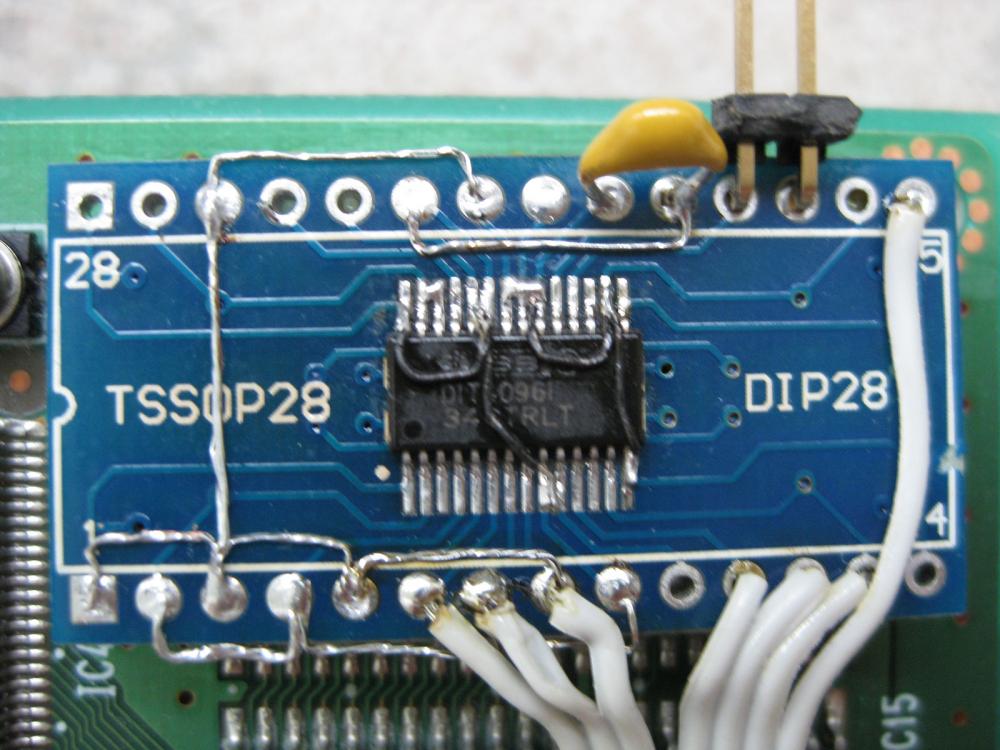

PARUS wrote:I reviewed XR385, DB50XG, SW60XG boards and found that on XR385 there is AK4510 DAC (and on MU10 also) but on DB50/SW60 there is […]

Show full quote

I reviewed XR385, DB50XG, SW60XG boards and found that on XR385 there is AK4510 DAC (and on MU10 also) but on DB50/SW60 there is another DAC NEC D63200.

Here are datasheets:

http://www.ym2149.com/mu10_spdif/ak4510.pdf

http://www.alldatasheet.com/datasheet-pdf/pdf … C/UPD63200.html? - unfortunately not English

Now I think about pins matching on AK4510 and D63200, exactly MCLK, L/R, SCLK and SDTI (AK4510). I think that

MCLK (AK4510) is similar CLK (D63200)

L/R (AK4510) - LRSEL/RSI (D63200)

SLCK (AK4510) - LRCK/WDCK (D63200)

SDTI (AK4510) - SI/LSI (D63200)

Is it right? Has anybody some ideas?

It depends, the UPD63200 has two different bus modes. When the 4/8FS SEL pin is high, then the 63200 has two audio data input pins, and thus is not compatible. But, if the 4/8FS SEL pin is low, then it has one data input pin and is potentially compatible.

SI (LSI) is serial audio data input, like SDTI on AKM.

LRCK (WDCK) is left/right clock input, like L/R on AKM.

CLK is serial bit clock, like SCLK on AKM. On both chips, rising edge latches data pins in.

LRSEL (RSI) in this mode is just configuration pin, LRSEL=low, then LRCK works same way than on AKM, left channel serial data is sent during LRCK high.

There is no matching pin for AKM's MCLK, as the UPD63200 does not need a Master Clock.

Then there is another config pin on UPD63200 that defines if it should take last 16 or last 18 bits when LRSEL changes. AKM takes only last 16 bits in when L/R changes.

Is this of any help?