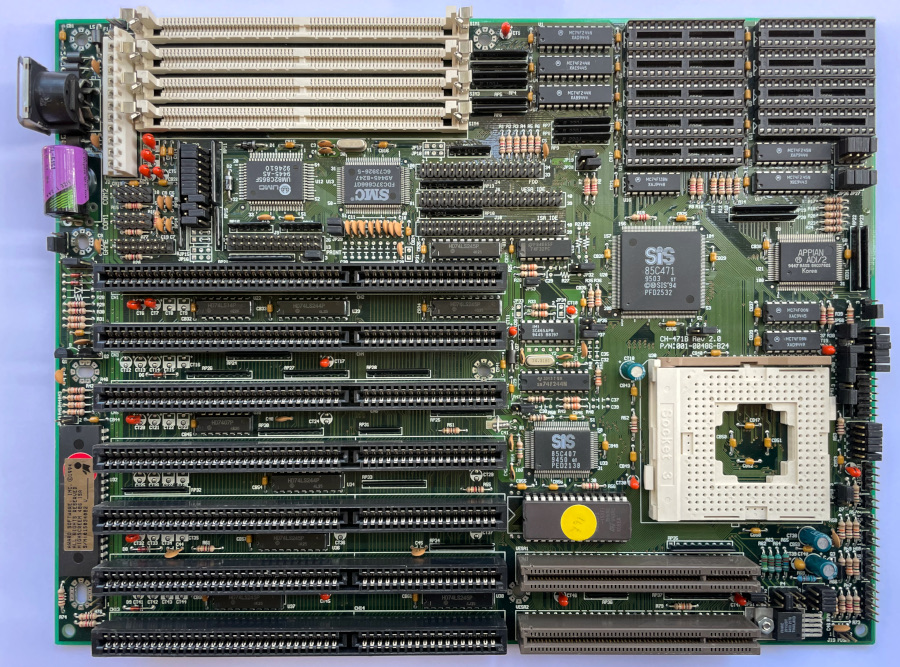

Chicony CH-471B rev 2.0 based on SiS 85C471 - one more item to the list of 486 motherboards with 1024Kb L2 cache.

The fastest classic ISA/VLB motherboard.

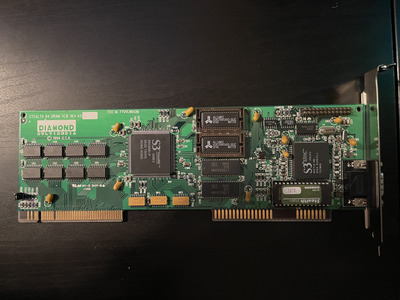

Didn't think i will ever see Ark1000VL and S3 Trio64 video cards ticking reliably at 66MHz base frequency with the CPU running at 200MHz.

Some impressive results in interactive DOS graphics and Windows GUI because of that.

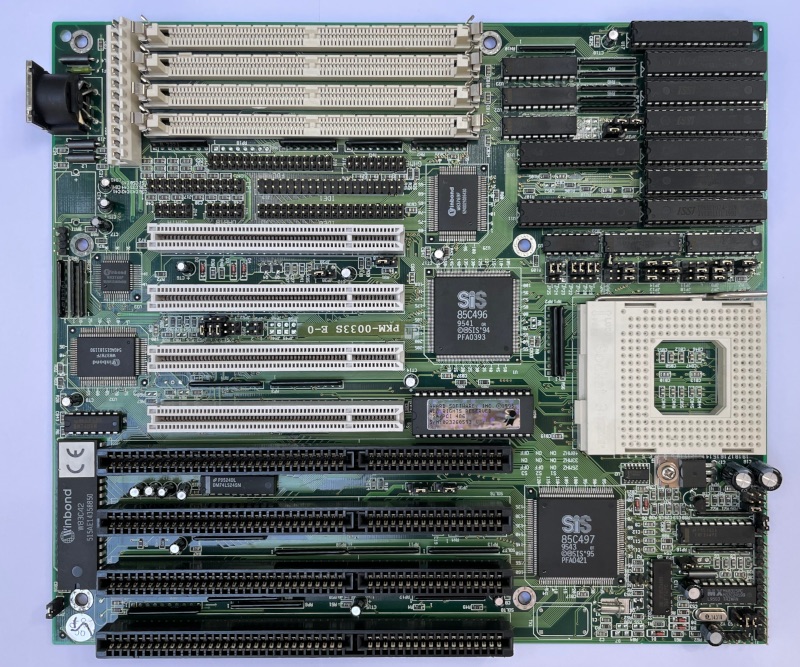

It also looks badass:

An unique assembly for 486 ISA/VLB class hardware.

There is an on-board Appian ADI/2 EIDE controller with integrated driver in the BIOS.

For reference, one of the best EIDE controllers from that time - the Adaptec AVA-2625VL is relabled ADI/2 silicon.

So we have a cool Adaptec EIDE on board.

Support for 4 drives (only 2 of them VLB EIDE, the other 2 are standard IDE interface), 2 floppies, 2 COM and 1 LPT ports.

Clock generator and jumpers cover the full range of frequencies - 25, 33, 40, 50, 60, 66, 80 MHz.

The large amount of through-hole components suggests early/mid design and release date.

Not very pretentious about L2 cache chips.

Took a moment only to find working configuration.

Something that is simply not granted for 1Mb L2 cache buffer with tight wait states.

Jumper setup is a bit messy. Took a while to figure out the configuration for Am5x86.

Most manuals online are incorrect or don't list the processor entirely.

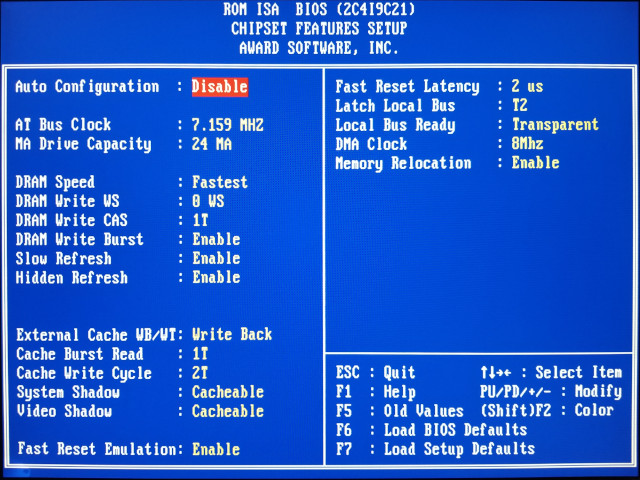

Picture above shows a working setup.

Am5x86's level 1 cache is stuck in write-through mode. The corresponding pin is connected to GND somewhere in the middle layers of the PCB.

Used the simple adapter from this post to enforce WB mode.

If ISA BUS SPEED is set to anything but 7.159 MHz (BIOS parameter) the keyboard controller starts missing strokes.

No support for EDO RAM. Something expected for this chipset.

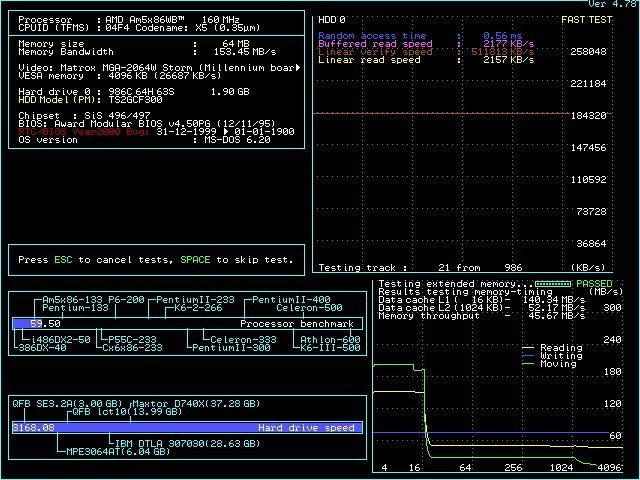

--- Am5x86 at 160MHz (4x40)

All BIOS settings on max.

Ark1000VL requires LOCAL BUS READ = SYNCHRONIZE and CACHE BURST READ = 2T (1T is best) which results in lowered overall performance.

Used Diamond's S3 Trio64 instead.

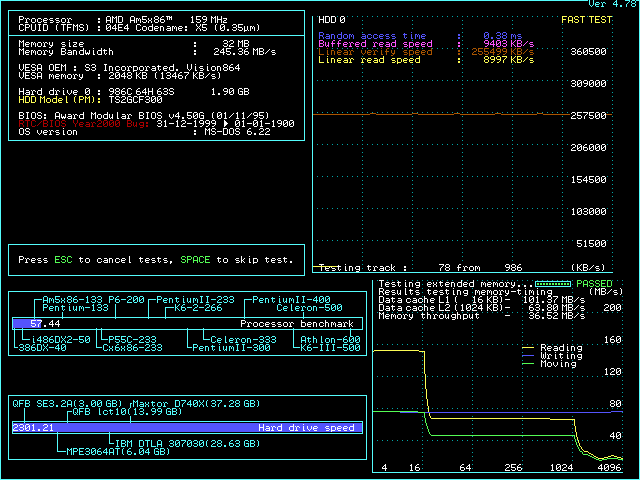

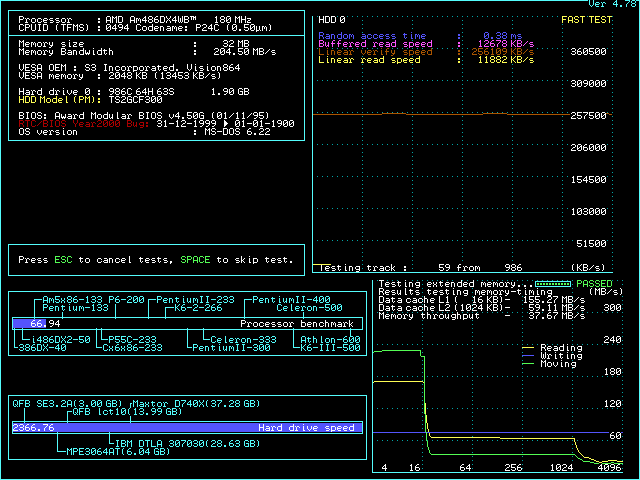

SpeedSys reports great metrics.

One of the best on-board IDE controllers - on par with Asus PVI.

Nice memory and L1/L2 cache numbers.

benchmark results

While slower than Asus VLI and PVI this is still an excellent 486 motherboard.

Very satisfying experience.

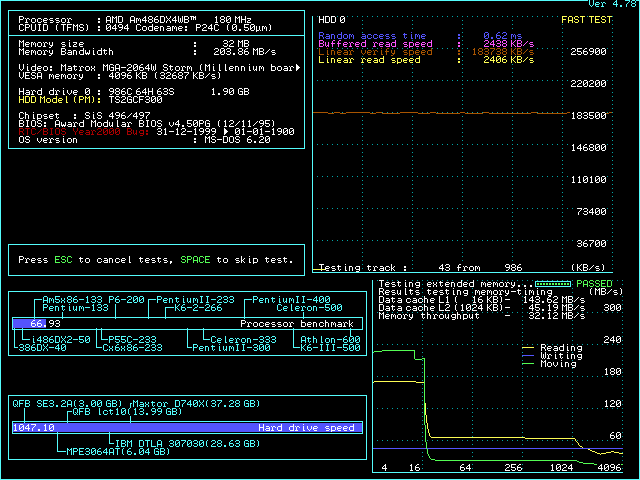

--- Am5x86 @ 180MHz (3x60)

All BIOS settings on max, except:

DRAM SPEED = SLOWER (best is FASTEST)

CACHE BURST READY = 2T (best is 1T)

LOCAL BUS READY = SYNCHRONIZE

A nice side effect of the last 2 parameters (mandatory for 180 and 200 MHz) is that Ark1000VL works and produces better performance for DOS interactive graphics than S3 Trio64.

First time seeing Ark1000VL and S3 Trio64 ticking reliably at 60MHz.

S3 Trio64 managed with 0 wait state while Ark1000VL required its wait states to be set to 1.

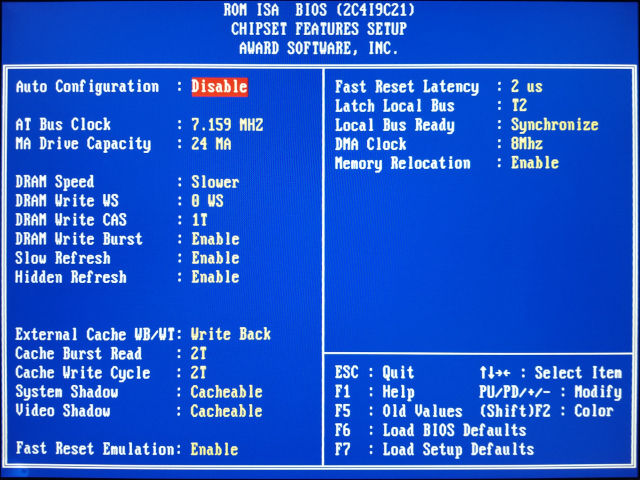

BIOS:

Speedsys:

Used Ark1000VL for DOS interactive graphics and S3 Trio64 for Windows accelerated GUI.

In some cases background panels in Windows GUI can get pixel corruption with the S3 Trio64 card running at 0-waits.

benchmark results

While not quite on par with later 486 designs, it is impressive for an ISA/VLB system.

But it only gets better ...

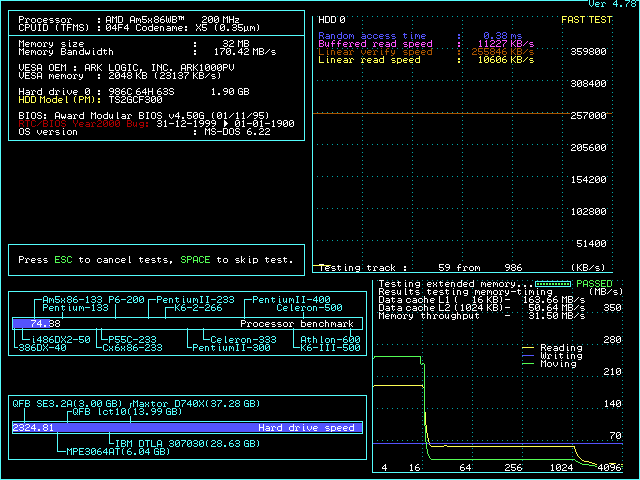

--- Am5x86 @ 200MHz (4x50)

Same BIOS settings and notes from the 3x60 configuration.

Ark1000VL runs at 0-wait states here.

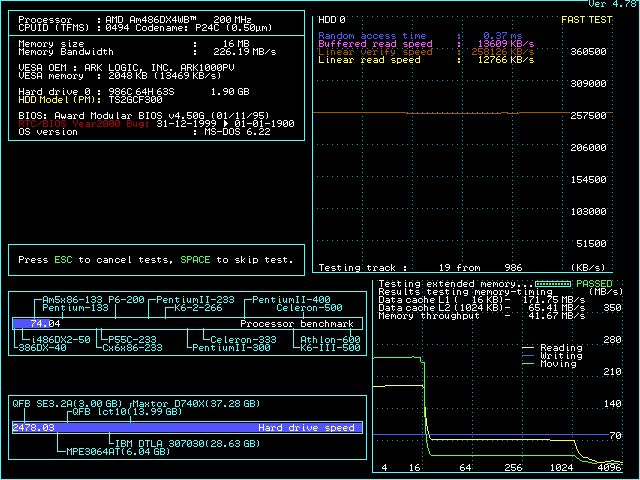

Speedsys:

Used Ark1000VL for DOS interactive graphics and S3 Trio64 for Windows accelerated GUI.

In some cases background panels in Windows GUI can get pixel corruption with the S3 Trio64 card running at 0-waits.

Posting these separately, since this configuration is slower than 3x66, so results are not reflected in the combined charts.

While at 3x60 things were behind compared to later model 486 motherboards, at 4x50 DOS interactive graphics are on par, but still lacking in Windows accelerated GUI and complex offline compute.

It is hard to compete against LuckyStar D equipped with Voodoo3 in Windows, also SiS471 in general lacks at complex offline computation tasks compared to SiS 496/497.

Still, it is clear already that this is a very fast classic ISA/VLB motherboard.

But it does not stop here ...

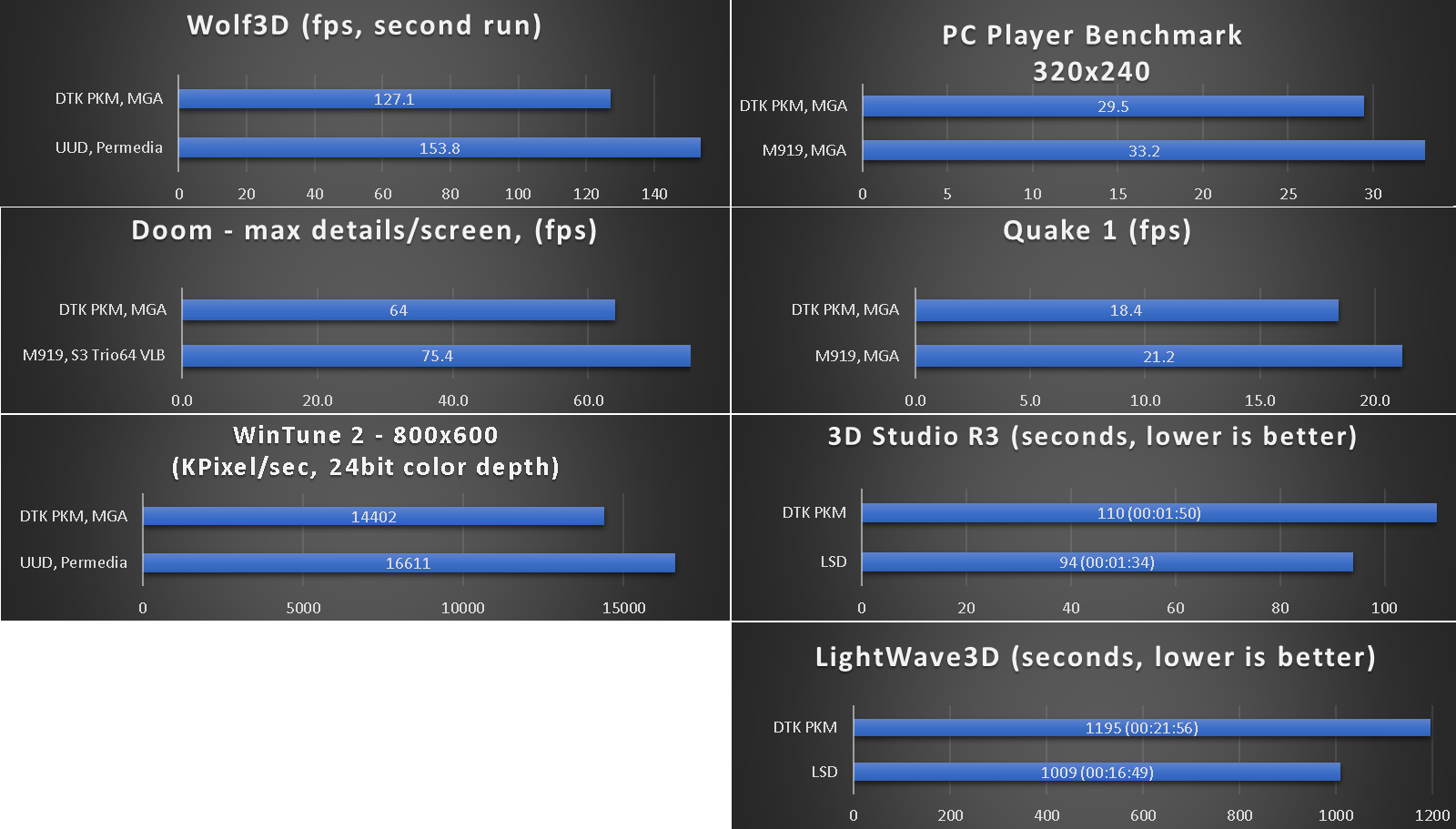

--- Am5x86 @ 200MHz (3x66)

Same BIOS settings and notes from the 3x60 configuration.

DOS interactive tests pass with 32Mb RAM, some of the more complex tests pass with 24Mb, but proper stability is achieved with 16Mb RAM only.

Se la vie.

Speedsys:

Used Ark1000VL for DOS interactive graphics and S3 Trio64 for Windows accelerated GUI.

In some cases background panels in Windows GUI can get pixel corruption with the S3 Trio64 card running at 0-waits.

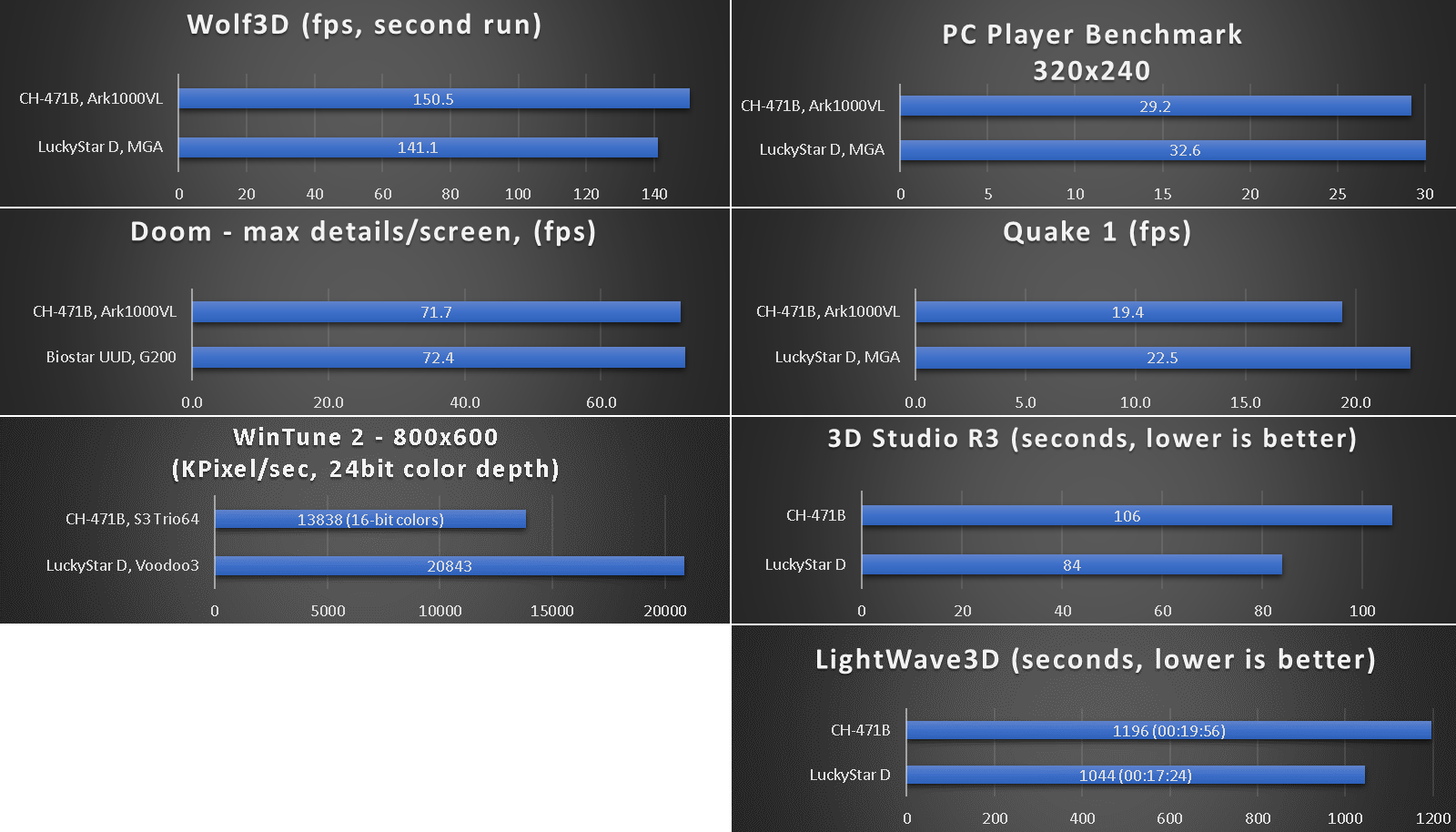

benchmark results

So, what are we seeing here ?

The fastest ISA/VLB system. That's for sure.

Not the fastest clock-to-clock motherboard but its ability to overclock to 3x66MHz without bus dividers places it in a class of its own.

In addition:

The best Wolf3D score to date.

The best Doom score to date.

In general, this guy is starting to take on LuckyStar rev:D in the 200MHz department. Not bad at all.

Of course LSD can go much further on a narrow overclock, but we are talking complete stability here.

--- POD100

Updated the big POD100 post with information about this motherboard.

Short summary:

Things worked mostly as expected.

Intermediate performer.

Using trial and error discovered that jumper 29 in position 2-3 forces the L1 cache in WB mode.

Unfortunately in this configuration the system becomes unstable.

No wonder the manual lists same jumper configuration for P24D and P24T processors, where L1 cache is in WT mode.

---

While the integrated EIDE, multi I/O controllers and 60/66MHz capable clock generator are interesting features on their own, its performance at 160MHz is nothing to brag about.

What makes this assembly truly unique is its ability to handle 200MHz just fine. As mentioned above, so far this is the only SiS 471 based system that can do it with complete stability in place.