Hi Vasco, I will try to answer your questions.

For any Intel or AMD CPU with internal cache WB capability, the 471 chipset DACK1*/DACK0* CPU Type select hardware trapping should be a logical ‘1’ on both pins. The SiS471 reference manual page 21 only mentions P24D/P24T for this setting, but it is also needed for the DX4-100&EW and the AMD Enhanced Am486DX2, Enhanced Am486DX4, and Am5x86-P75 CPUs.

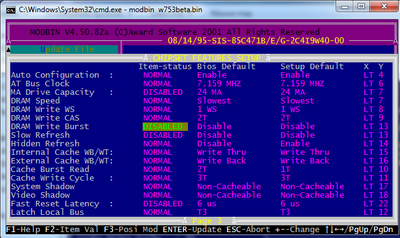

Then the BIOS, I’ve checked the CPU string list, the CPUID table and the Reset_ID table in the W735BETA.BIN BIOS and they look correct for this 08/1995 Award BIOS. Except for the Am5x86-P75, all ‘modern’ 486 CPUs are supported.

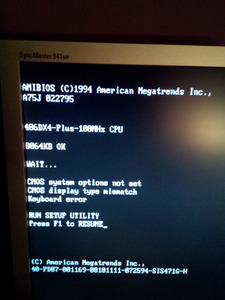

So your 486DX2-66&EW should be indicated as P24D, but the 80486DX2-S indication tells me this CPU is in WT mode! You should be able to confirm this with a CPU Identification tool like my CHKCPU.

Note that this BIOS shows the “Internal Cache WB/WT:” option in the BIOS Setup only for the P24T and for Cyrix CPUs.

For the P24D (486DX2WB), iDX4WB, and Am486DX2WB/DX4WB, this 08/14/95 BIOS can detect if these CPUs are in WB mode and programs the chipset registers accordingly. It then hides the “Internal Cache WB/WT:” option, because user interaction for this automatic function is not required.

So, you only have to find the correct jumpers for L1 WB mode and the BIOS takes care of the rest. 😉

Jan