Reply 20 of 48, by Deunan

Garrett W wrote on 2021-04-21, 08:42:Do you think it would be a good idea to replace the SRAM chips, even though they seemed to run 100% fine when using the Intel 386 at 40MHz?

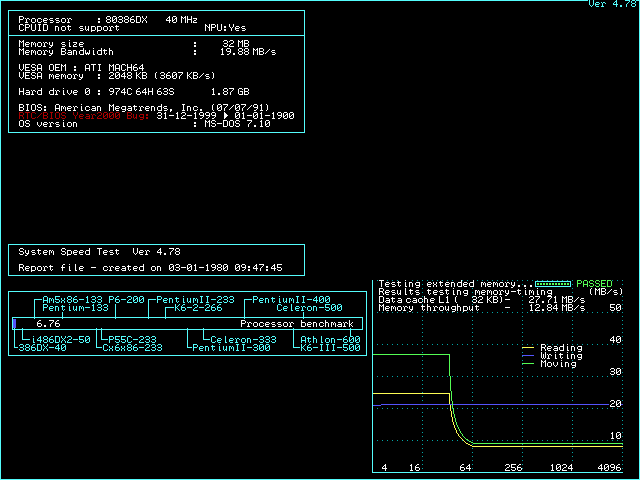

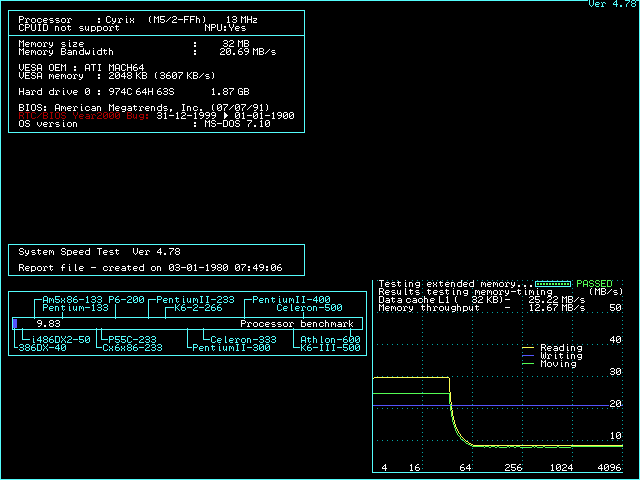

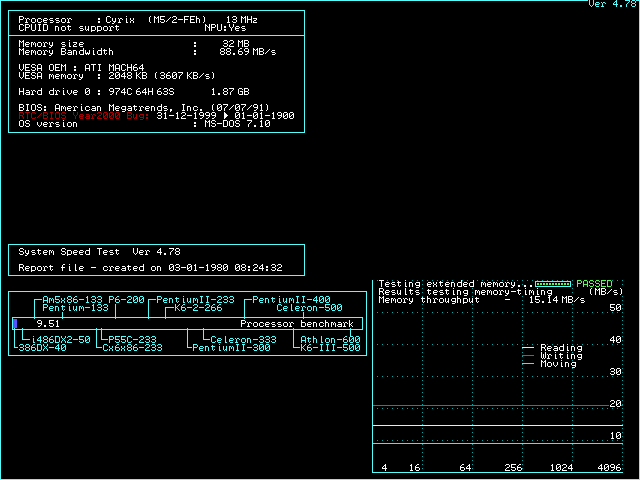

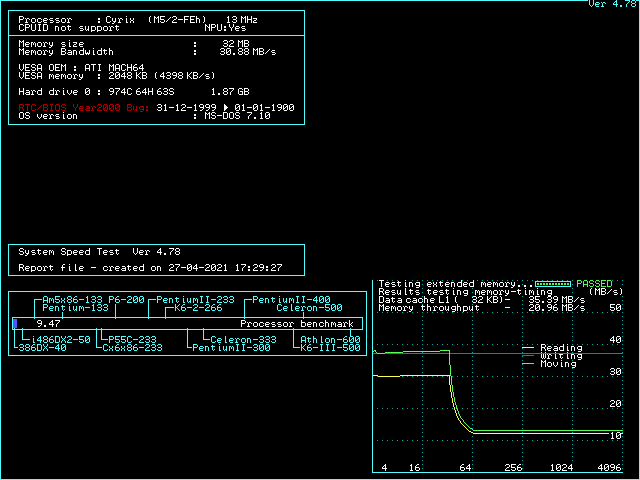

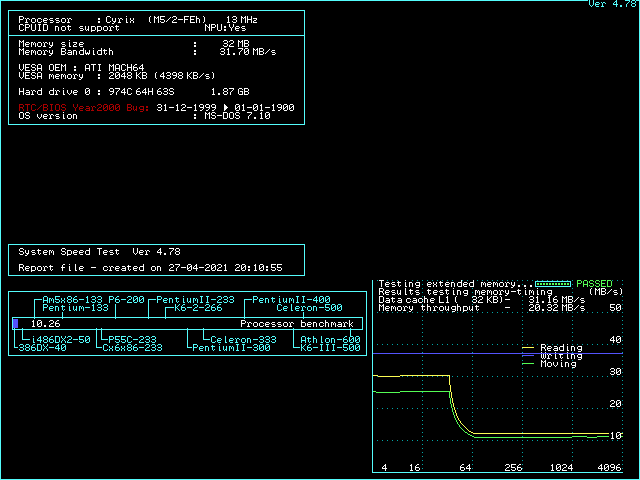

Usually 20ns chips are not fast enough to run at 40MHz with 0WS. You need 15ns, and preferably a 12ns tag chip as well - it all depends on the chipset and quality of signal routing. Some mobos might even need 10ns, especially if you intend to populate both banks. This BTW might not be a good idea, you gain a little but possibly loose a lot by having to go +1WS. Though CPUs with on-die cache tend to gain more from bigger (even if slower) external cache then 386.

You got lucky with 386, the SRAM chips are probably much better than 20ns and the access patterns are way diffgerent (386 will mostly fetch code while DLC chips, even with their small cache, can do semi-random data fetches while in a loop - can't quite recall the numbers but 1kB is already over 80% hit rate). That being said with elevated temperature even that 386 will eventually glitch and crash, maybe you didn't test it long/hard enough to notice.