First post, by jasa1063

- Rank

- Oldbie

I pose that question in the title of this post because that is exactly what I asked myself the first day I got this computer in November 2020. I did set one limit on this in that there would be no modifications to the motherboard itself. The motherboard is a Biostar MB-1340MKA-F with a MACRONIX MX83C305FC/MX83C306FC chipset. This is an interesting chipset that contains an integrated 8K cache which is advertised to work as well as a 64K external cache. From my testing this is validated.

The system came with the following components:

AMD 386DX/40 CPU

5MB 70ns 30-Pin SIMMs

Multi I/O ISA controller (Serial, Parallel, Gameport, IDE & Floppy)

Trident 9000I - 512K SVGA ISA card

3.5" 1.44MB floppy drive

5.25" 1.2MB floppy drive

Here is what I have done for upgrades:

TI486SXL/40 CPU (The motherboard is designed to accept an Cyrix/TI 386 upgrade chip with no need for an interposer)

Cyrix FasMath 387DX/40 Math Coprocessor

32MB 60ns 30-Pin SIMMs

SIIG Cirrus Logic CL-GD5429 SVGA 2MB ISA video card

Sound Blaster 16 CT2800 ISA sound card

3Com 3C509B 10Mbs ISA network card

XTIDE card with 386 XTIDE BIOS (BIOS is shadowed for maximum performance)

Compact Flash to IDE adapter with 2GB Compact Flash card running DOS 6.22 with Windows 3.11

Using the 60ns memory I was able to the CAS values for read and write to 2 in the BIOS and also setup hidden refresh. I was able to find the DOS utilities for the CL-GD5429 one of which was a small program to change the clock speed from 50MHz to 57MHz. I set AT Clock divider to 4 for a 10MHz ISA clock speed. Settings higher than this caused some stability issues. While the BIOS recognizes and configures the TI486SXL its default settings were not optimal. It enabled the Flush input but excluded all the memory from A000-FFFF from being cached and disabled the first 64K of each 1MB region from being cached as well. I was not that familiar with Cache Coherency in a 386 system so I had to some research. I found the following article and it does a great job going over what Cyrix did to deal with this issue.

https://www.os2museum.com/wp/386-cache-coherency/

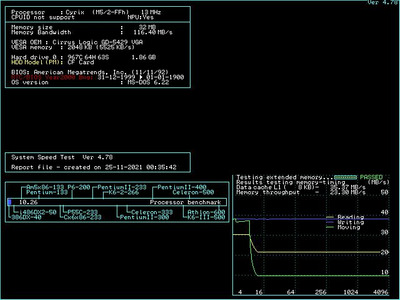

Using utilizes written by Paul Gortmaker, I made changes to the caching options and only excluded the A000-BFFF address blocks. I also enable caching of the first 64K of each 1MB region. The issue with the last option is that the A20 input has to be enabled on TI486SXL, but doing so on my system gave me an A20 hardware error when trying to this. I went back into the BIOS settings and turned off A20 emulation and that fixed the problem. The result of doing all this has given me what I consider to be the best possible outcome for a computer like this. There are higher performance options like clock doubled Cyrix 386 upgrades as well as IBM Blue Lightning, but sticking with the 40MHz clock of this board ruled that out as those are based on 33MHz or lower clocked boards. So how does the system perform? Winbench 3.11 score comes in at 18 million plus change and included are the results from Speedsys 4.78.

I welcome any suggestions or comments on how I could further improve on what I have done already.