Interesting reading:

https://www.bswd.com/pciide.pdf

3.1. Device Operation with Older BIOSes

PCI IDE controllers that follow this specification and are added into a system that has an older BIOS that is

not aware of this specification will behave as follows:

If the device defaults to 'compatibility' mode, it will hard decode the compatibility addresses and use the

compatibility IRQs. If the system already contains an IDE controller some unusual behavior will occur.

The end-user will have to deal with the problem.

If the device defaults to native-PCI mode, it will be configured like any other PCI device and will operate

(with the appropriate drivers) without end-user involvement.

4.0. Compatibility Interrupt Connection

This document does not define how a PCI IDE controller on an add-in card gets connected to the

'compatibility' IRQs (14 and 15) needed to operate in 'compatibility' mode. It is unlikely that these IRQs

will ever be made available on the standard PCI connector. However, it is the responsibility of the add-in

card to provide these connections in some manner.

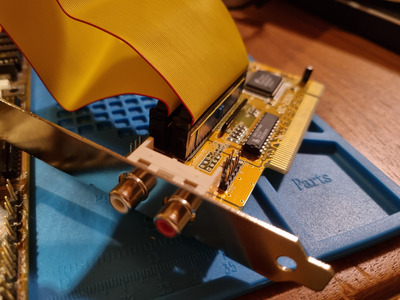

Chapter 4.0 "Compatibility Interrupt Connection" - describe the use of a so called "paddle board" to connect to IRQs 14 and 15 - this is most likely what applies in my case.

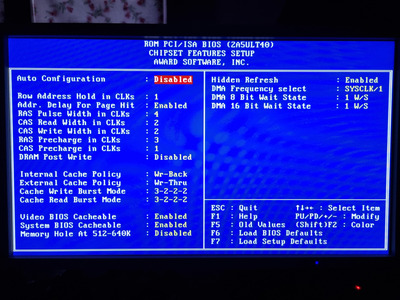

I doubt the BIOS on this board have any knowledge about Native-PCI mode. Maybe something for the BIOS decompiling aficionados out there to investigate 😀

What I do know is that the 82C822 is wired for IRQ 14 and 15.

So my guess would be that, for example the Promise Ultra 133 TX2 PCI IDE controller can only operate in Native-PCI mode. Or this would maybe be irrelevant since it is carrying its own ROM? But it simply prompts that "no drives are detected and thus no BIOS routines will be loaded".

Edit:

This thread also covers the perils with early PCI revisions and the crappy PCI IDE controller support:

Re: What are the Early PCI implimentation issues.

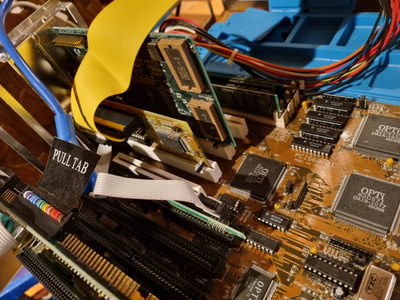

Which have even further inspired me to try out the first / upper PCI slot-1 / slot-A (not to be confused the CPU board slots with the same name).

Just have to remove the battery since it is interfering. Fun fact is that the Tekram DC-290N PCI IDE controller (which is on the way) does not interfere with the CMOS battery - coincidence - or by design? 🤔