First post, by Tronix

- Rank

- Member

Hello,

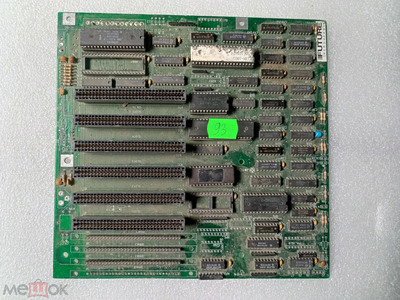

I recently got this motherboard (photo by seller):

I identified the board as Jaton JXM-1003 aka JXM-JET 88-V2 and found some jumper info here: Re: 8088/XT Clone Motherboard - Keyboard Not Working

As you can see, the board is missing: power connector, keyboard connector, tantalums, resistors in some places, quartz and crystal oscillator, trimmer capacitor, i8284, i8288, dip-switch, PLS connectors for connecting LEDs/jumpers, one slot for sipp module, delay line . And the most important component - PAL16L8.

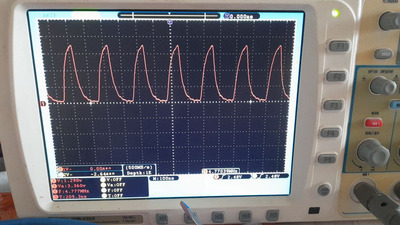

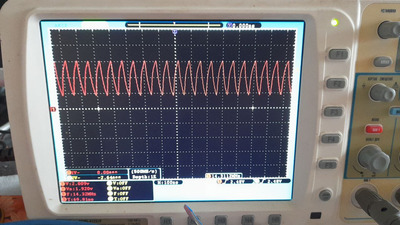

So, i restored power and keyboard connectors, installed i8284, crystal and crystal generator and fixed OSC and CLK clocks

Then i put the socket and stuck the i8288 bus arbiter, along the way restoring several tracks above and below it;

Fixed RESET by soldering all sorts of diodes / capacitors in the J4-J3 area;

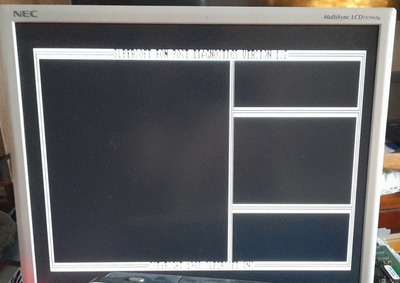

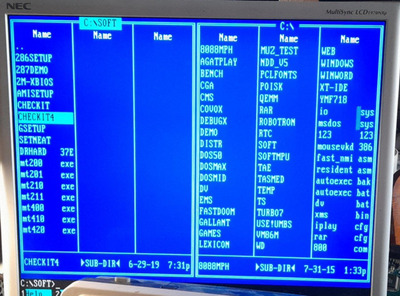

Burn in 2764 EEPROM Landmark Diagnostic ROM, started the board with CGA card and got first signs of life:

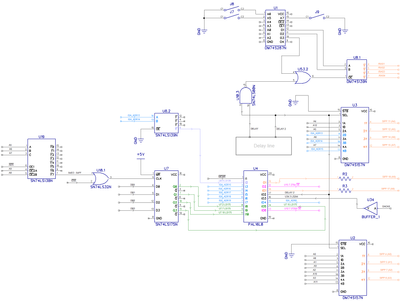

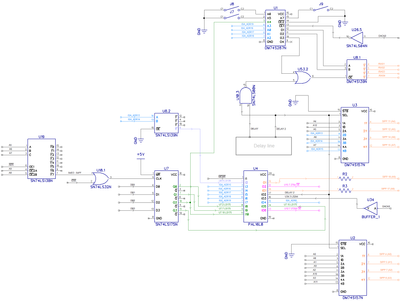

Encouraged by the success, I replaced the SIPP holders with SIMM30 holders and approached the main problem - the lack of PAL16L8. Using a multimeter, I tried to draw a section of the circuit around PAL16L8 :

I tried to write this equations for PLD logic:

"INPUT PINS!MEMR PIN 1;!A13_A14 PIN 2;A15,A16,A17,A18,A19 PIN 3,4,5,6,7;D0,D1,D2,D3 PIN 8,9,11,14;A8 PIN 15;DACK PIN 16;MPX PIN 17;"OUTPUT PINS!CS1,!CS2 PIN 12,13;MA8,MA9 PIN 18,19;EQUATIONSCS1 = A19 & A18 & A17 & A16 & A15 & A13_A14 & MEMR & DACK;CS2 = A19 & A18 & A17 & A16 & A15 & (!A13_A14) & MEMR & DACK;WHEN (MPX) THENMA8 = (A16 & DACK) # (A17 & !DACK);ELSEMA8 = A8;WHEN (MPX) THENMA9 = (A18 & DACK) # (A19 & !DACK);ELSEMA9 = 1;

This allowed the system to boot DOS 5.0 from XT-IDE, but almost no applications run. Doesn't start Volcov Commander, CheckIt, Cats game etc... I'm not sure that I correctly described the logic of the PLD, so I ask for your help.