tikoellner wrote:Asynchronous (jp 10 to 1-2): 62.5 (Superscape);

Synchronous (jp 10 to 2-3): 55.5 (Superscape),

So, asynchronous seem considerably slower.

Doesn't the larger number correspond to faster?

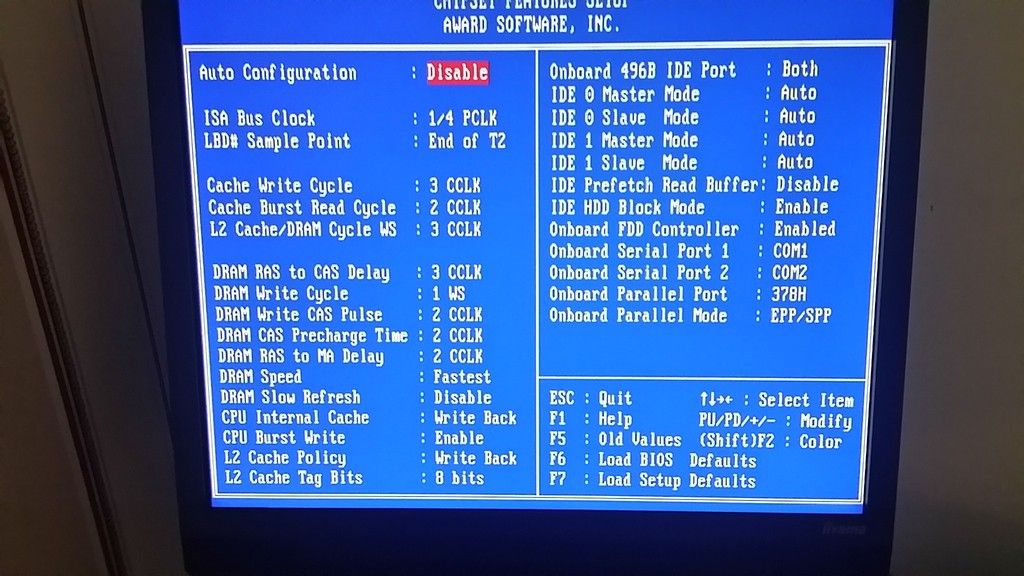

These are the settings I use if I have a 33 MHz FSB on a SiS496 chipset,

Cache Write Cycle = 2

Cache burst read cycle = 1

L2 Cache/DRAM Cycle WS = 2

RAS to CAS = 3

DRAM Write Cycle = 0

DRAM Write CAS Pulse = 2

DRAM CAS Precharge Time = 1

DRAM RAS to MA Delay = 2

DRAM Speed = Fastest

CPU Internal Cache = Enabled

CPU Burst Write = Enabled (I recall this doesn't work with the Am5x86, but works with Cyrix 5x86)

L2 Cache Policy = Write-Back

L2 Cache Tag Bits = 7 bits (or set to 8 bits if L2 cache policy is Write-through)

IDE Prefetch Read Buffer = Enabled. Doesn't this speed up IDE access quite a bit when using the onboard IDE controller? However, I recall that many motherboards have issues with this setting.

I am able to get away with these settings if using an Am5x86-160 and a 40 MHz FSB, however if I use and IBM 5x86-120, cache burst read cycle and/or L2 cache/DRAM Cycle WS needed to be slowed down. Using single-banked cache also generally requires slower timings when running close to the stable limits like this.

On my DTK PKM-0033S motherboard, if I am using an IBM 5x86c-120 with 512 KB double-banked cache, I was able to use cache write/cache read/DRAM cycle of 2/1/3. When using 512 KB single-banked cache, I had to slow it down to 2/2/3.

On a different SiS496-based motherboard I have, which is single-banked cache only, you may want to look at this thread, Help with SiS 496/497 Tomato 4DPS 486 motherboard

I will cut the relevant sections from it,

I am tyring to get this system setup, with an AMD X5-160 ADZ at 40x4. […]

Show full quote

I am tyring to get this system setup, with an AMD X5-160 ADZ at 40x4.

At 40 MHz FSB, setting the cache write cycle to 2 and DRAM Speed to Fastest gives really nice cachechk speeds:

L1 Read: 165 MB/s

L2 Read: 75 MB/s

RAM Read: 51.5 MB/s

RAM Write: 83.6 MB/s

However the system is not stable in Windows. I need to set the cache write cycle up to 3 for the system to be stable enough in Windows to run the Quake 2 benchmark, or play mp3's continually.

Setting cache write cycle to 3 greatly lowers the Cachechk speeds as follows:

L1 Read: 165 MB/s

L2 Read: 75 MB/s

RAM Read: 39.4 MB/s

RAM Write: 55.7 MB/s

Keep in mind that the stability with cache burst read cycle and DRAM Cycle WS also depends on the RAM quantity and number of RAM sticks. If I were you, I would start out with a single stick of 32 MB FPM RAM and use the settings I noted above, namely cache write/cache read/DRAM cycle of 2/1/2. If you experience instability, set the DRAM Cycle WS to 3. Still not stable, set the cache burst read cycle to 2. Still not stable, try decreasing your DRAM Speed timing to Fast, then slower, then slowest.

On another SiS496-based motherboard, I noticed that for the IBM 5x86-120 to work well with DRAM Cycle WS = 2 that the CPU needed 3.60 V.

Concerning cache increases and performance boosts, I will copy/paste what I wrote in another thread,

32 MB (write-back)

1024K = 5.83

512K = 5.52

256K = 5.33 […]

Show full quote

32 MB (write-back)

1024K = 5.83

512K = 5.52

256K = 5.33

Interesting how CPUMark99 shows a 10% improvement when the cache jumps from 256K to 1024K. I think the real-world improvement is around 2%. Shows how sensitive this benchmark is in regard to cache. Similarly, the benefit of write-back over write-through cache was 4%.

Plan your life wisely, you'll be dead before you know it.