First post, by Benedikt

You probably already guessed it: This is another clone card.

To everyone that has been following the developments on this forum and knows this thread it is reasonably obvious that this is to a substantial degree based on a combination of picture-based reverse engineering, other people's picture-based reverse engineering and picture-based reverse engineering of a replica based on picture-based reverse engineering of the original card.

One implication is that this cannot be a simple replica but has to add significant value, because it would otherwise inevitably be perceived as a copycat project.

Furthermore, this latecomer has to be the card that Fagear's SSI-2001 from a couple of years ago is not -- and in as many ways as possible. A replica, but somehow different.

And the design goals for this card were a bit different, indeed, because (a) PCB prototyping has become even more affordable, so shrinking the board would only save a few cents, and (b) SID chips have become even less affordable, so the interest in cheap alternatives has grown significantly.

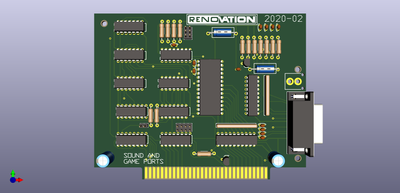

Point (a) makes an accurate replica feasible, while point (b) screams for a microcontroller-based solution. The Renovation SSI-2001 tries to be both.

It tries to mimic the original Innovation SSI-2001 as closely as feasible; modifications and additions have to be as unobtrusive as possible.

The modifications and additions are:

- A voltage regulator to provide 9 Volts for MOS 8580 compatibility

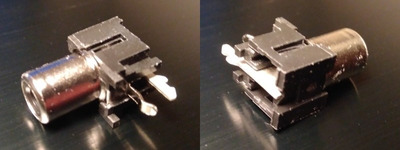

- The possibility to use two NE556 dual timers instead of a single NE558 quad timer for the joystick interface

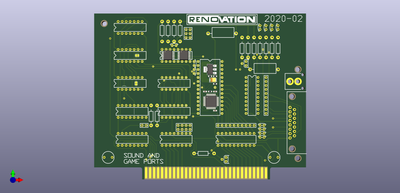

- The option to omit the expensive SID chips, entirely, and to use an STM32, instead

A card with the aforementioned changes can obviously only look like a reasonably accurate replica if these changes are somehow "invisible".

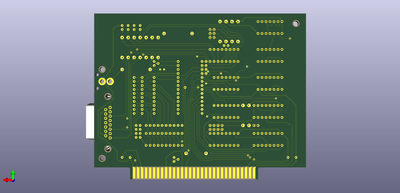

The Renovation SSI-2001 achieves this by hiding all additional footprints and most additional traces right where the vintage components normally go, so that they indeed become nearly invisible if vintage components are used.

Alright, enough of the rambling!

Here it is: The preliminary design of the Renovation SSI-2001 -- An Innovation SSI-2001 replica that can be built without vintage components

The STM32-based version could omit the clock divider and IO delay circuitry and thereby save four ICs.

As an added bonus, the STM32 with its ARM Cortex-M3 running at 71.5909 MHz (5x 14.31818MHz) might be fast enough to bit-bang S/PDIF using its internal DMA peripherals, but that is pure speculation.