Reply 260 of 283, by LocalBus

Sphere478 wrote on 2022-03-19, 09:37:See the p5a simple mod thread. […]

LocalBus wrote on 2022-03-19, 08:49:Maybe @Chkcpu can help out with some BIOS modifications 😀 […]

Sphere478 wrote on 2022-03-19, 02:01:Some bios editing utilities can enable hidden Settings. […]

Some bios editing utilities can enable hidden Settings.

Awdbedit I think is one, but I’m told it corrupts.

I think it would be really cool to make a socket 3 to socket 7 adapter.

We could be running dx4s in mvp3 and ali aladdin V boards :p

Maybe @Chkcpu can help out with some BIOS modifications 😀

Judging by the brochure for OPTi 571/572 it should indeed support "up to 2 MB of Write-

back cache".https://archive.org/stream/bitsavers_optibroc … e_1993_djvu.txt

I think the main thing holding this board back though, is the 32-bit DRAM bus.

The VLB-to-PCI might not help the cause either, but the main chipset design is just not keeping up.

When comparing benchmark results for # doom -timedemo demo3 (screen size maxed out), I get 2550 realtics. I bet a 430 chipset based P100 would have better results. Fun fact is that MBF204 runs significantly faster, where the same demo3 results in 1869 realtics = 40.0 frames per second.

Regarding 486 compatibility with this board (provided some kind of socket adapter) - I know @Snufkin looked into it. Might be some pins that would need to be hot-wired to the chipset since those are not present on Socket4, 5 or 7. Who knows, some day ...

See the p5a simple mod thread.

In that thread there is a way to toggle write back/write through with a hardware mod

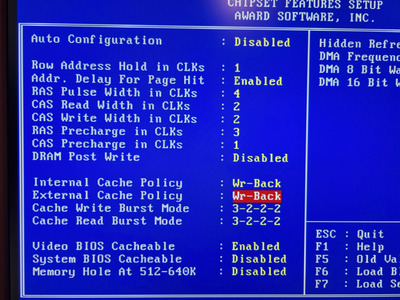

Thanks for sharing! Hmm, I wonder if pulling pin AJ19 high toggles both L1 and L2 cache to write-back mode? L1 is already set to WB and this is possible to change from BIOS (tested WT as well with less performance as a result).