First post, by maxtherabbit

- Rank

- l33t

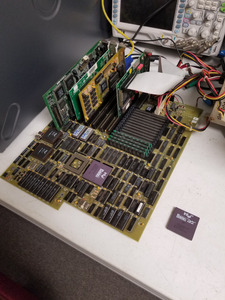

I've got a pretty neat 486 board here. Built in 1991, it uses a Zymos POACH chipset (designed for 286 systems) grafted to a 486 processor and cache with the help of a bunch of PAL/GALs and discreet logic.

My issue with it is that despite using an ET4000AX card which will manage >4MB/sec on a 286 system, I'm only able to get about ~2MB/sec throughput to video memory. This cripples an otherwise awesome board for gaming performance. So I am on a quest to improve the situation.

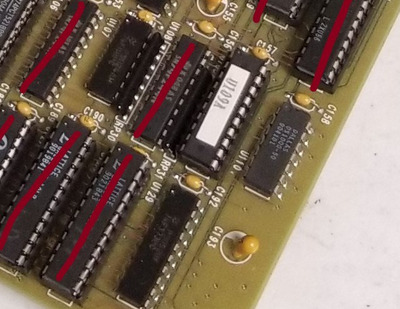

The POACH, being a 286 chipset, is designed to run at wire speed and does not offer any type of bus wait states or recovery cycles. Therefore, I can assume that the bus slowness is a factor of something in the glue logic. So far after conducting a brief survey of the components, the only thing that stands out at me is this: a Dallas DS1000-50 silicon delay line. I can't really think of another good reason for this to be present, so I'm considering removing it and shorting the input to the tap. Thoughts?