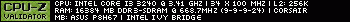

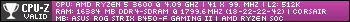

Janoz, I am very interested if you can run this board with 1024K, the tightest cache/memory timings, and 2x64MB FPM memory. If it is not too much to ask, a test with an AMD X5-133 and AMD X5-160 would be appreciated. L2 set to WB mode. I have a dead one of these boards, but I am using it as part of a reverse engineering process to add 1024K to my MB8433-UUD board. Please use HIMEM and Memtest 4.0, test #6 as a means to gauge stability. You can select just test #6 from within Memtest to speed up the process. Press 'C' when memtest starts to bring up the configuration menu.

The M915 uses a 22-ohm resistor pack between the cache addresses and the TAG addresses. The MB8433 has no resistor between these addresses. The DTK-PKM-0033S uses a 72F244 buffer between each, while the HOT-433 uses some unknown UM8002 chip. While I can route the MB8433-UUD to use 1024K cache with 0-ohms between cache and TAG addresses very easily, I cannot use 2-1-1-1 cache timings with an X5-133. I need to reduce the speed to 3-1-1-1 with 2x64 MB of RAM, however I can use 2-1-1-1 with 512K, single-banked, and 2x64MB of RAM. Naturally, I want to use the fastest timings. The DTK-PKM board, though based on the SiS496/497 chipset, can use 1024K, 2x64MB, X5-160, all on the fastest timings. That design uses the buffers between each cache address and the TAG address. Basically, if your M915, which is based on the UMC chipset like the MB8433, can get away with just a 22 ohm resistor pack between the cache and TAG address and works on the fastest settings w/1024K and 2x64 MB RAM, then that is the simpler design I will use on my modified MB8433.

Thanks a lot!

Plan your life wisely, you'll be dead before you know it.