Tried the debug command on the latest Award BIOS and it returned 00 with it set to Write-Back.

Same for when it is set to Write-Through.

This Jan '96 1.7 really hates the older Award BIOS that came on my April '95 1.7 board. L1 and L2 cache are super sketchy about working... Set the L1 to Write-Back and the L1 completely goes away. Set the L2 to other than default timings and it goes away.

The AMI BIOS that came on the Jan '96 board has the same L1 bug where it has to be set to disabled for it to be enabled.

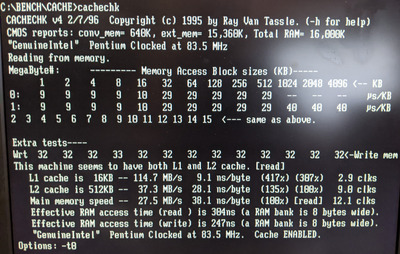

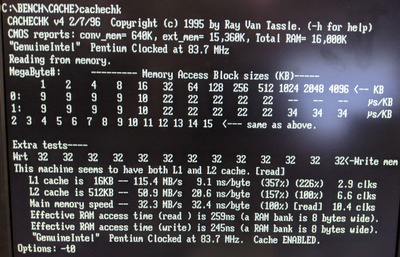

Running debug with the AMI BIOS that came with the Jan '96 board:

Settings in BIOS:

L1 Enabled

Write-Back

Result - 40

cachechk does not see L1 cache and results seems to indicate it is disabled

L1 Enabled

Write-Through

Result - 40

cachechk does not see L1 cache and results seems to indicate it is disabled

L1 Disabled

Write-Back

Result - 20

cachechk sees L1 cache and results seems to indicate it is enabled

L1 Disabled

Write-Through

Result - 20

cachechk sees L1 cache and results seems to indicate it is enabled

Some something is definitely screwy with either the BIOS or the chipset... My guess is the BIOS.

I still can't get the supposedly newer AMI BIOS to work even with this newer board when using the 1Mb EEPROM.