Thanks Deunan for the info and baseline to test against. I ran with 128K cache enabled and 1ws and got this..

CACHECHK V7 11/23/98 Copyright (c) 1995-98 by Ray Van Tassle. (-h for help)

CMOS reports: conv_mem= 640K, ext_mem= 7,424K, Total RAM= 8,064K

386 Clocked at 39.0 MHz

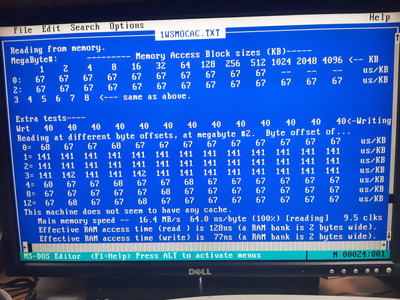

Reading from memory.

MegaByte#: --------- Memory Access Block sizes (KB)-----

1 2 4 8 16 32 64 128 256 512 1024 2048 4096 <-- KB

0: 39 39 39 39 39 39 39 39 90 90 -- -- -- us/KB

2: 39 39 39 39 39 40 40 40 90 90 90 90 90 us/KB

3 4 5 <--- same as above.

6: 39 39 39 39 39 40 40 39 90 90 90 90 -- us/KB

7: 39 39 39 39 39 40 40 40 90 90 90 -- -- us/KB

8: 39 39 39 39 39 40 40 39 90 -- -- -- -- us/KB

Extra tests----

Wrt 47 47 47 47 47 47 47 47 47 47 47 47 47<-Writing

Reading at different byte offsets, at megabyte #2. Byte offset of...

0= 39 39 39 39 39 40 40 40 90 90 90 90 90 us/KB

1= 79 79 79 79 79 79 80 79 128 128 128 128 128 us/KB

2= 79 79 79 79 79 79 79 79 129 128 128 128 128 us/KB

3= 79 79 79 79 80 79 79 80 128 128 128 128 128 us/KB

4= 39 40 39 39 39 40 40 40 90 90 90 90 90 us/KB

8= 39 39 39 39 40 40 40 40 90 90 90 90 90 us/KB

12= 39 39 39 40 39 40 40 40 90 90 90 90 90 us/KB

This machine seems to have one cache!? [reading]

!! cache is 128KB-- 27.9 MB/s 37.6 ns/byte (228%)

>>>> If you think you do have L2 cache, you might have FAKE CACHE chips! <<<<

5.6 clks

Main memory speed -- 12.2 MB/s 85.8 ns/byte (100%) [reading] 12.8 clks

Effective RAM access time (read ) is 171ns (a RAM bank is 2 bytes wide).

Effective RAM access time (write) is 89ns (a RAM bank is 2 bytes wide).

386 Clocked at 39.0 MHz. Cache ENABLED.

Options: -t0 -z

Disabling cache and enabling 0ws resulted in this..

CACHECHK V7 11/23/98 Copyright (c) 1995-98 by Ray Van Tassle. (-h for help)

CMOS reports: conv_mem= 640K, ext_mem= 7,424K, Total RAM= 8,064K

386 Clocked at 39.0 MHz

Reading from memory.

MegaByte#: --------- Memory Access Block sizes (KB)-----

1 2 4 8 16 32 64 128 256 512 1024 2048 4096 <-- KB

0: 54 54 54 54 54 54 54 54 54 54 -- -- -- us/KB

2: 54 54 54 54 54 54 54 54 54 54 54 54 54 us/KB

3 4 5 6 7 8 <--- same as above.

Extra tests----

Wrt 33 33 33 33 33 33 33 33 34 33 33 33 33<-Writing

Reading at different byte offsets, at megabyte #2. Byte offset of...

0= 54 54 54 54 54 54 54 54 54 54 54 54 54 us/KB

1= 113 113 113 113 113 113 113 113 113 113 113 113 113 us/KB

2= 113 113 113 114 113 113 113 113 113 113 113 113 113 us/KB

3= 114 113 113 113 113 113 113 113 113 113 113 113 113 us/KB

4= 54 54 54 54 54 54 54 54 54 54 54 54 54 us/KB

8= 54 54 54 54 54 54 54 54 54 54 54 54 54 us/KB

12= 54 54 54 54 54 54 54 54 54 54 54 54 54 us/KB

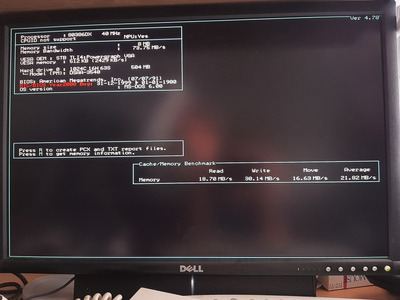

This machine does not seem to have any cache.

Main memory speed -- 20.4 MB/s 51.3 ns/byte (100%) [reading] 7.6 clks

Effective RAM access time (read ) is 102ns (a RAM bank is 2 bytes wide).

Effective RAM access time (write) is 63ns (a RAM bank is 2 bytes wide).

386 Clocked at 39.0 MHz. Cache ENABLED.

Options: -t0 -z

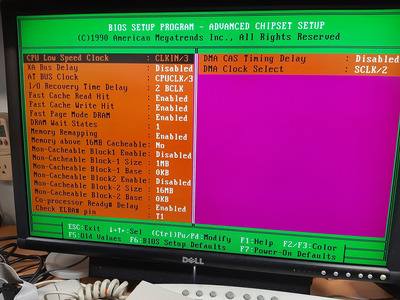

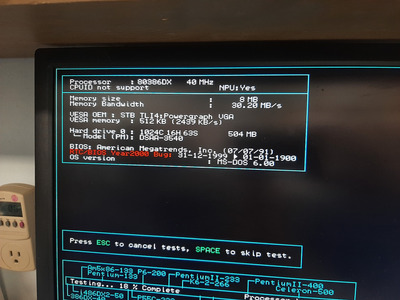

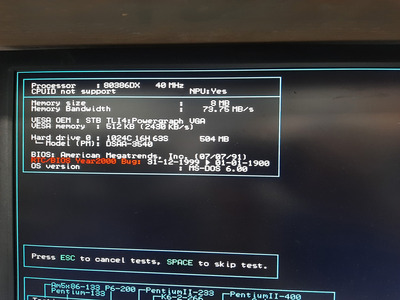

I tried disabling the fast read and write hits and it didn't change anything unfortunately. It seems like the /3 on the bus has been running okay, but time may tell for the hard drive corruption. Had to swap out several I/O cards til I found one that worked well enough at that speed. I also have the option to go down to /2 on the bus, but I haven't had any luck getting that stable. On a whim I set the divider up to 5 but that didn't help @ 0ws.