Reply 300 of 613, by keenerb

I fired off an email to James Pearce about the lo-tech memory board; I'm not sure it was intended to COMPLETELY replace on-board memory, or if that's even possible.

I wouldn't think that the xi8088 bios would have any special checks for on-board vs. on-bus memory in bios startup.

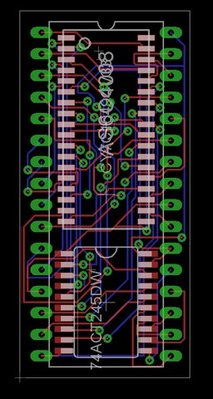

Sergey did mention using a separate memory board rather than the on-board memory. I wonder if disabling the chip enable lines on the while leaving everything else connected could have any impact; I could pop out the memory chip, straighten out that leg, and re-insert.

Another thing that's curious (to me) is that A19 is connected directly to CE on chip 1, but A19 is filtered through a lot of logic on "Memory Chip Select" side. On the lo-tech board, both chips have their own select logic. Is there any chance both chip 1 and 2 could have CE enabled at the same time, or that the delay the additional logic introduces on chip 2 causes data to be retrieved from chip 1 instead, because it responded first? It may be that the select logic only sets CE low on U12 when CE is high on U11, and vice-versa, I can't really tell for sure reading the schematic.

I noted previously that simple memory errors were obvious fairly frequently where : would be ! in a batch file.

:start

xdir

goto start

This simple test inevitably fails. I'd get the error that it couldn't find the label "!start" after X repetitions, but of course it wasn't always !start, it might be "$dir command not found" or "goto stert", but one character (or more) would eventually be wrong.