First post, by mpe

Trying to upgrade my Triton II based motherboard (GA-586HX 1.55) to get cacheable RAM > 64M.

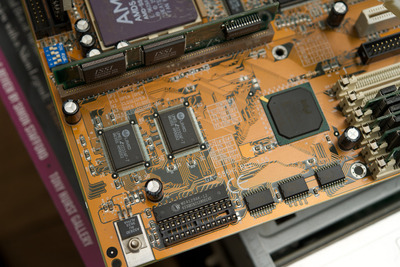

In stock config there is 256kB L2 cache and one 16kx8 SRAM TAG chip onboard + one empty 28pin socket.

Both of my COAST modules are 256kB and they have their own TAG SRAMs:

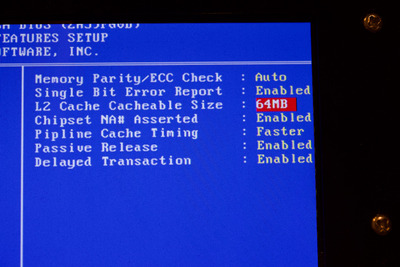

So when I put one of these in the COAST slot, I'll get 512kB L2, however the cacheable range is still only 64M.

There is a BIOS setting that flips between 64M and 512M. However, the board doesn't POST when I set this to 512M no matter if with COAST module or not. I was hoping the chipset would use the extra tag on the COAST to get the extra cacheable range, but it doesn't seem to be the case.

So I am wondering I need to put something to the free SRAM socket. Unfortunately, I don't have a 16kx8 12ns chip, but I have abunch of 32kx8 15ns which should be compatible AFAIK. However, when I put this one in the board doesn't even start.

Any idea how to get this working? Do I need some sort of special tag chip?