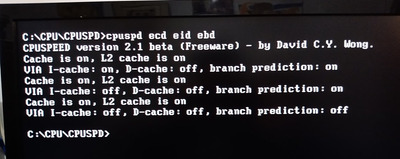

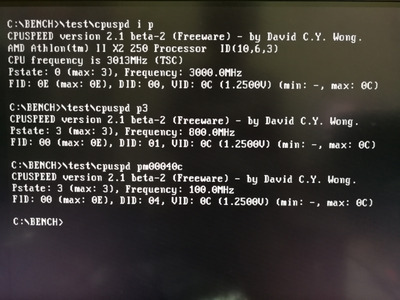

Ok here it is. This version includes K10 P-states control. Please note that there might still be bugs. During my testing, sometimes first few settings won't set the p-state properly and the system might reboot, and then it works after a few times (I have no idea why).

[Edit: I've since added a small delay after setting the p-state (for command pm[xx]), which seems to be stable after a few tests. More thorough testing needed.]

(Version 2.1 beta-2)

- Filename

- CPUSPD.EXE

- File size

- 265.95 KiB

- Downloads

- 8 downloads

- File license

- Fair use/fair dealing exception

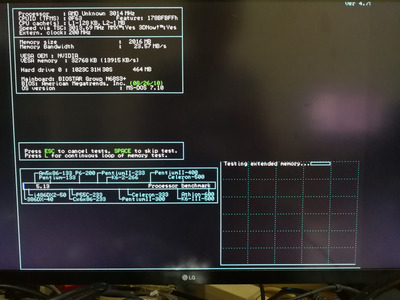

I've only tested it on 2 systems:

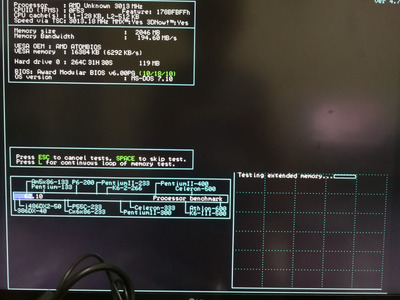

Biostar N68S3+ v6 with Athlon II X2 250

Gigabyte GA-770T-D3L with Athlon II X2 440

Intel's p-sate is implemented but not tested.

AMD family 15h (FX cpus, i.e. Bulldozer, Piledriver) could probably work for earlier models (00-0fh), I'd checked the datasheet and the MSR registers are similar with K10, but I'm not sure as I don't have any such systems. If you could test it out, I would be very interested to know the results.

Transmeta p-state is implemented but not tested. Please note that Transmeta cpus could only change p-state but not setting them (at least that's what appeared to be in the public docs).

P-states are the power saving states of the CPU. The higher the p-state the lower the power.

So for a CPU with 4 states:

P0 (most power/fastest) --> P3 (least power/slowest)

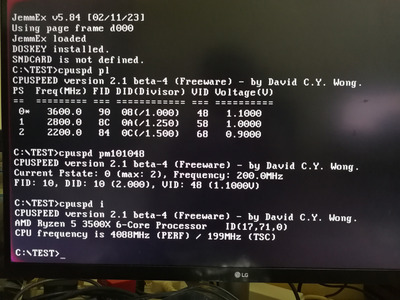

For AMD K10 cpu you could modify the Fid, Did, and Vid of a p-state.

P-state commands:

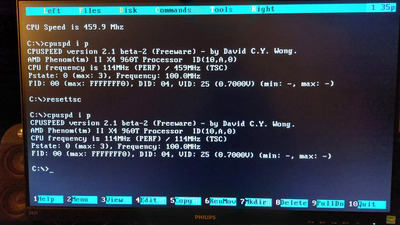

p[x] - display CPU p-state if run without any parameters, or switch current p-state to x, where x is 0-7 in decimal.

pm[xx] - set current CPU p-state value to xx, where xx is 0-15 in decimal for Intel, or ffddvv in hex for AMD (must be 6 digits).

Where,

ff = FID value in hex (00-3F) - Freq ID: PLL frequency multiplier relative to reference clock (6-bit).

dd = DID value in hex (00-04) - Divisor ID: post-PLL divisor to reduce the operating frequency. 00 = divide by 1, 01 = divide by 2, 02 = divide by 4, 03 =divide by 8, 04 = divide by 16

vv = VID value in hex (00-FF) - Voltage ID: voltage level (please see formula below).

For AMD, the value for the pm command must be 6 digits.

CPU voltage is calculated with this formula:

If VID >= 20h, voltage = 0.7625V - 0.0125V * (VID-20h);

else voltage = 1.550V - 0.025V * VID;

For example:

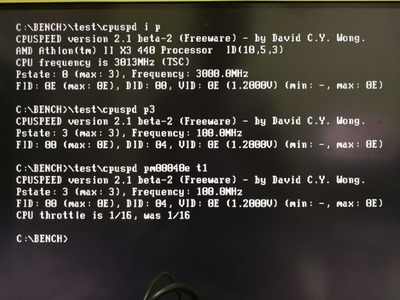

CPUSPD i p (display current p-state, it defaults to P0 when booted up)

CPUSPD p3 (switch current p-sate to P3)

CPUSPD pm00040c (edit current p-state, P3, to FID=0, DID=04, VID=0C)

To revert back to original speed is very easy, you just switch back to P0. To slow down again, switch to P3 (or whichever p-state of your choice).

CPUSPD p0 (revert to original speed)

CPUSPD p3 (slow down again)

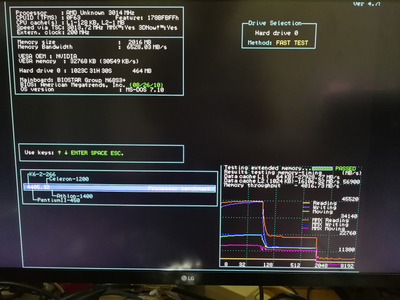

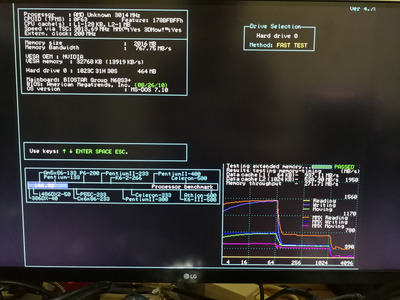

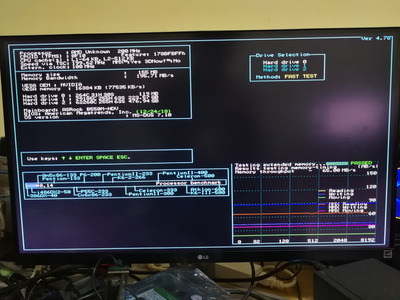

Gigabyte GA-770T-D3L with Athlon II X2 440:

Slow down your CPU with CPUSPD for DOS retro gaming.