Reply 200 of 251, by kalohimal

Version 2.1 released. Please download from post #1.

What's new:

- Bug fixes for VIA C3 D-cache control commands.

- Added p-states control for AMD K10 cpus (Athlon II, Phenom II, etc).

Note:

Commands moved:

For D-cache: cdd/cde => ecd/ece

For I-cache: cid/cie => eid/eie

How to use p-state controls:

P-states are the power saving states of the CPU. The higher the p-state the lower the power.

So for a CPU with 4 states:

P0 (most power/fastest) --> P3 (least power/slowest)

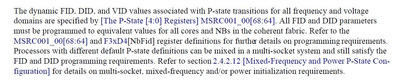

For AMD K10 cpu you could modify the Fid, Did, and Vid of a p-state.

P-state commands:

p[x] - display CPU p-state if run without any parameters, or switch current p-state to x, where x is 0-7 in decimal.

pa - list all p-states set up by BIOS.

pm[ffddvv] - set current CPU p-state value to ffddvv in hex for AMD (must be 6 digits).

Where,

ff = FID value in hex (00-3F) - Freq ID: PLL frequency multiplier relative to reference clock (6-bit).

dd = DID value in hex (00-04) - Divisor ID: post-PLL divisor to reduce the operating frequency. 00 = divide by 1, 01 = divide by 2, 02 = divide by 4, 03 =divide by 8, 04 = divide by 16

vv = VID value in hex (00-FF) - Voltage ID: voltage level (please see formula below).

For AMD, the value for the pm command must be 6 digits.

CPU voltage is calculated with this formula:

If VID >= 20h, voltage = 0.7625V - 0.0125V * (VID-20h);

else voltage = 1.550V - 0.025V * VID;

For example:

CPUSPD i p (display current p-state, it defaults to P0 when booted up)

CPUSPD p3 (switch current p-sate to P3)

CPUSPD pm00040c (edit current p-state, P3, to FID=0, DID=04, VID=0C)

To revert back to original speed is very easy, you just switch back to P0. To slow down again, switch to P3 (or whichever p-state of your choice).

CPUSPD p0 (revert to original speed)

CPUSPD p3 (slow down again)

Please note that TSC is tied to p-state 0 by hardware. So if your games/apps need accurate TSC, please use p-state 0.

Slow down your CPU with CPUSPD for DOS retro gaming.