Version 2.2 released. Please download from post #1.

What's new:

- Bug fix for PIIX4 "clock control enable" not set in throttle.

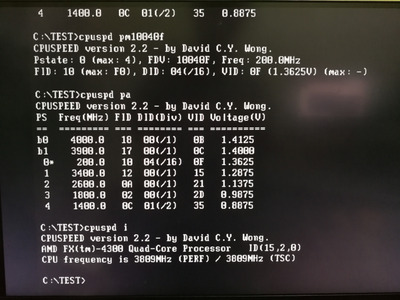

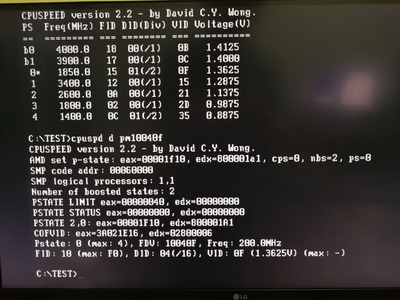

- Improved SMP codes to better support AMD K10 cpu (and beyond).

- Improved robustness of ACPI search codes which will hopefully eliminate protection faults reported for some motherboards.

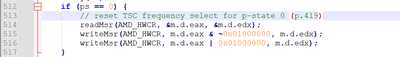

- Improved p-state functions to respect boosted p-states for AMD K10 (and perhaps future AMD cpu families).

- Correctly report error when CPU doesn't support hardware p-state (HWP).

- Cleanup VIA Esther codes.

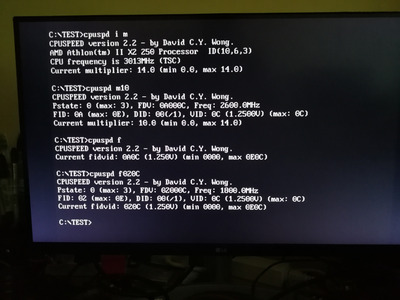

- Multiplier (m) and fidvid (f) commands now works for AMD K10.

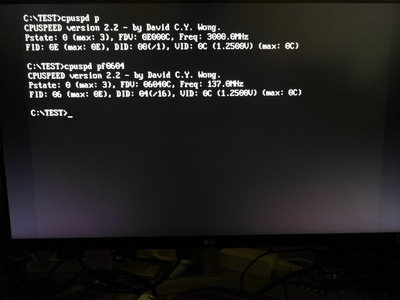

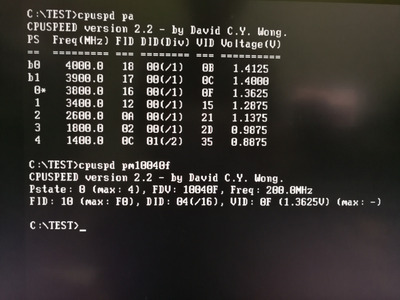

- Added FDV (Fid, Did, Vid) values display for the 'p' command for AMD K10.

- Added 'pe' command for AMD K10, to allow changes to Fid, Did and Vid for other p-state. (Note: I'd forgotten to include this in the readme.txt and the program's help. Will do that in the next version, but for now this command will work.)

- Added 'pf' command for AMD K10, to allow changes to Fid and Did only without affecting Vid.

- Added 'tf' command to use the south bridge database file 'cpuspd.sbi' first before attempting ACPI search for throttling. Normally the program will first attempt to use ACPI to find the throttle port, and switch over to the database file only when ACPI search failed.

The 'm' and 'f' commands work as previously, i.e. m[x] sets the multiplier in decimal, and f[ffvv] sets the fidvid (ffvv is 4 digit hex value, where ff = fid and vv = vid).

cpuspd m12 <-- sets multiplier to 12.

cpuspd f040C < -- sets fidvid to fid=04 and vid=0C.

The 'tf' command is identical to 't', except for using the database file:

cpuspd tf <-- shows current throttle, but setup throttle port using database file instead of ACPI.

cpuspd tf4 <-- sets throttle to 4, but setup throttle port using database file instead of ACPI.

Note: the ‘min' and 'max' are values reported by the cpu. Since K10 is not locked, it is possible to set values beyond 'max' (overclocking/overvoltaging).

Important note: Changing Vid is risky as severe over voltage might damage the cpu. For K10 the Vid value is inversely related to voltage, i.e. smaller Vid results in higher voltage!

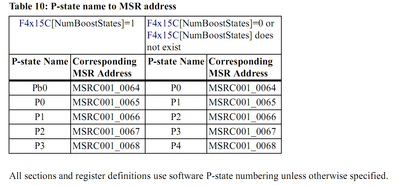

'cpuspd p' will now display the FDV value (Fid, Did, Vid), to provide this information at a glance (please see picture below).

How to use 'pf' command:

pf[ffdd] - modify the Fid (frequency multiplier) and Did (frequency divisor) for the current p-state, leaving Vid alone. ff = Fid and dd = Did in hex. ffdd must be 4 digit hex.

For example:

cpuspd pf0604 < -- will set multiplier to 6 and divisor to 4.

How to use 'pe' command:

pe[nffddvv] - modify the Fid (frequency multiplier), Did (frequency divisor), and Vid (voltage) for the specified p-state. n=p-state number to change, ff = Fid, dd = Did, and vv = Vid in hex. nffddvv must be 7 digit hex.

For example:

cpuspd pe206040C < -- will set p-state P2's multiplier to 6, divisor to 4, and voltage to 0C.

Commands that are no longer needed and removed: tx, xp

Cheers and have fun.

Slow down your CPU with CPUSPD for DOS retro gaming.