First post, by FrankieKat

I have an original IBM EGA adapter that's experiencing some issues switching between resolutions - 320x200 ("Mode 1") and 640x350 ("Mode 2"). I am using an MCE2VGA adapter since I do not have an actual EGA monitor. First off, I have tried two DB9 cables, and have verified continuity between all 9 pins from the solder pins on each PCB so confident that there is no connection issue. I have also tried a different EGA card (a later "Paradise") which has no problems switching between resolutions with the MCE2VGA. I also have no problems using the MCE2VGA with a CGA and an MDA card, so that points to the IBM card as the source of the trouble.

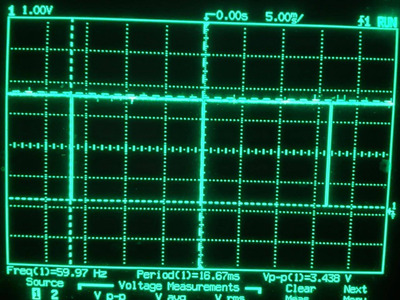

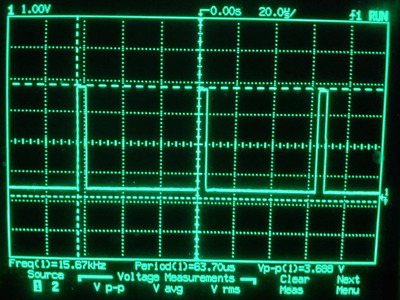

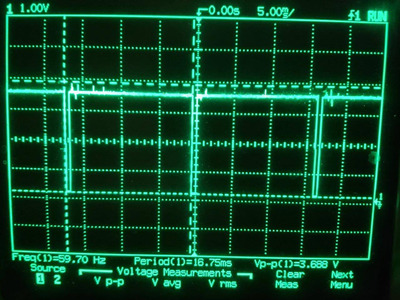

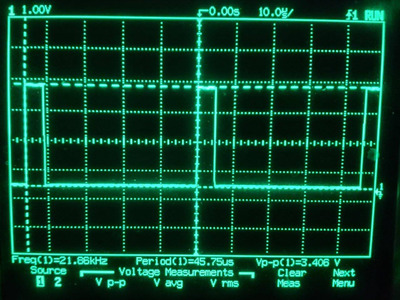

What happens is that the "monitor" stays in the 640x350 mode but continues to work and generate the correct graphics but is displayed out of sync and with incorrect color as you might expect. It's easy to see this on the MCE2VGA since there are LEDs that display the resolution that is currently being used - so the 640x350 LED (right most) will stay lit. It has worked correct from time to time, though I haven't been able to observe any correlation as to when/why. Otherwise it works perfectly and reliably in 640x350, both text and graphics.

There is one clue that I've seen and that is that there is a 74LS86 (quad XOR) gate chip (U8) on the schematic that gets very hot - measured at 153 degrees Fahrenheit. This gate appears to be used in the Horiz and Vertical SYNC and polarity circuit, and connects to the Horiz and Vertical pins on the DB9 output (via a 74LS244 buffer and a resistor). I checked for shorts between the gates on 86 and 244 and the resistor values and everything is okay there. It would seem odd that this temperature would be normal operating behavior, though I do not have another IBM EGA to compare. Near as I can tell, it's the only chip that's heating.

Any thoughts, ideas or tips would be appreciated. Obviously this EGA card is a rare beast, so would really like to see it repaired and working.

Thanks!

FK