First post, by Haz939

Hello,

I wonder if anyone can help me? I'm trying to essentially build an 486 SBC computer using the SIS85C471 chipset. The computer will interface through a 16 bit ISA interface and will have the bare minimum of components for it to work. The video, sound, serial and IDE drive connections will be from pre-existing ISA cards.

I think I'm off to a good start, however I'm having some confusion on how to implement the bus transceivers (74245) I think I've correctly connected the ones for the SD0 bus and XD0 bus from the datasheet and block diagram. It doesn't give much information or an application note on how they should be connected.

There is also some transceivers for the address bus but I can find no mention in the datasheet on how these should be connected, no enable and dir pins for the 74245 like there is for the data bus. My best guess that these signals must connect to the processor.

This is the part of the datasheet that mentions the control and enable signals for the 74245 transceiver and block diagram.

https://drive.google.com/file/d/1wSpw27KvH5ry … iew?usp=sharing

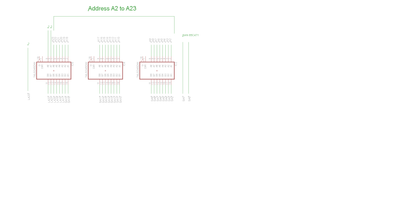

This is my quite crude eagle schematic:

https://drive.google.com/file/d/1wZNo4Xg030tF … iew?usp=sharing

Link to the full SIS85C471 datasheet.

https://www.datasheets360.com/pdf/805338928285727440

Many thanks for any help 😀