Sphere478 wrote on 2022-02-18, 05:16:

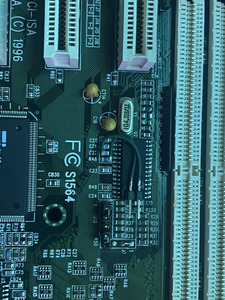

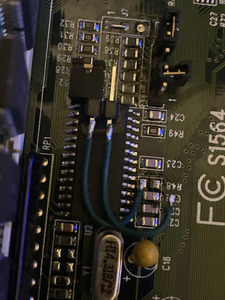

R48

I got 4.7v on both sides which is what my atx2at shows on the 5v rail

Sorry it took a while to get this to ya. Apologies.

No worries, but that 4.7/5V bothers me a bit. We're fairly sure, based on the voltage you measured on C20 (goes to pin 1) and the resistance to ground of all the Vcc pins, that all the chip power pins are at 3.3V. I'm pretty sure that all the clock gen chip datasheets I've seen have a maximum input voltage for logic inputs of Vcc+0.5V. So in this case the input voltages shouldn't be higher than 3.8V. I don't know why they've pulled it to 5V. Given it hasn't broken then the standard clock gen chips must be fine with 5V on the inputs and the datasheets are just using the standard absolute maximums.

More modern chips are probably less tolerant of that though. So to be on the safe side, any adapter will probably want to clamp the OE and FSel pins to maximum 3.3V. Not certain how best to do that. Series resistor and then a low voltage Schottky diode to Vcc, or 3.3V zener to Ground, maybe? Or just not use them at all, though I had thought it would be nice to still be able to use the existing jumpers to select frequencies.

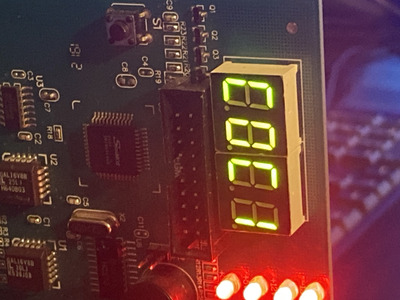

Thought just occurred to me, which I don't know that answer to, about power sequencing. Power comes up and the board is initially held in reset. Various things start to happen, including the board getting a Power Good signal from somewhere (PSU, on board voltage monitoring?) and oscillators start oscillating. I think I remember reading that some CPUs (I think 386 / 486) need a stable clock for a number of cycles before reset is released. It's possible that the board doesn't check the clock and just assumes that it will have become stable some fixed time after power good has been signaled, and so it releases reset a fixed time (time to stable oscillator + CPU wait) after power good.

If it does just wait a fixed time then there could be a problem with using a programmable clock gen. It's going to take a bit of time to program the chip after power comes up, by which time maybe the board will already have released reset. If it does, then the CPU won't have the pre-reset release cycles.

Might not be a problem. I could be misremembering about the CPU clocking requirements, or the programming would be fast enough to not matter, or (even if I have remembered correctly) the CPU is actually fine. If it is a problem then the new clock gen could be wired in to the board reset, so that it can hold on to reset until it's ready. But that starts to get away from it being a drop in replacement.