Baoran wrote on 2022-04-24, 19:21:I am building socket 7 system. CPU is K6-III+ and currently set to 5.5 x 66Mhz. Motherboard is SY-5EMA+ that has MVP3 chipset, 1 […]

Show full quote

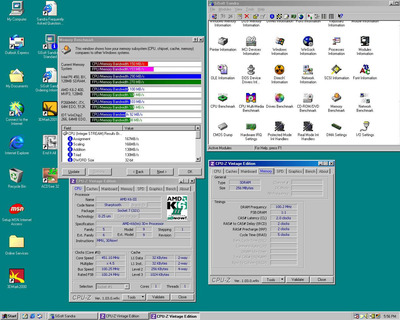

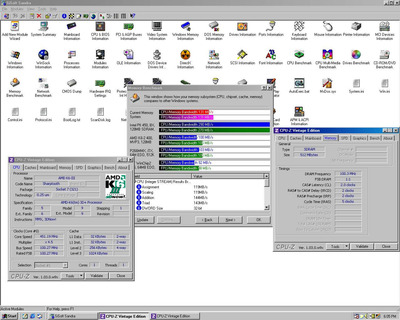

I am building socket 7 system. CPU is K6-III+ and currently set to 5.5 x 66Mhz. Motherboard is SY-5EMA+ that has MVP3 chipset, 1024KB of L3 cache and there is currently 2x256MB ram sticks installed.

I have been trying to find out clear information on effect of cacheable ram but I have found some conflicting information.

Is it that if I remove one of the ram sticks the performance should improve because all ram would be cacheable or is it because of the L2 cache on the cpu that there should be no change performance?

Like I read about 8bit tag in MVP3 chipset and it being limited to 256MB cacheable ram, but then there is also that L2 cache on the cpu mixing things.

Basically the sources are both right:

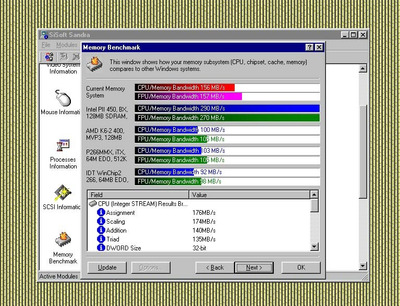

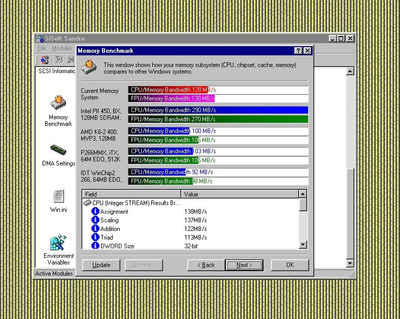

- staying inside cachable limit will maximize performance because all memory can be cached by motherboard cache.

- on a K6plus with on-die L2 cache, the impact of L3 cache on the motherboard is so small as to be considered negligible.

If you're running benchmarks and care about absolute highest score to last decimal, get thet RAM back inside cachable limits. If not, you're not going to notice anything either way.

Just to complicate matters, consider that in everyday use the biggest bottleneck on a system (by far) is storage performance, and if you use all that extra RAM to do a lot of disk caching, the benefit of that will far exceed the tiny difference in raw memory performance.

Another factor is operating system. Win9x in particular is dumb and tends to load its most used bits into uncached RAM. There's a patch for that though, see here: http://www.redline.ru/~ipl/win2cache_eng.htm

So, bottom line: probably won't matter noticeably with a CPU with its own cache controller able to cache everything. However it's also true that this much RAM is pretty nonsensical on a system like this, unless you're doing something very specific, so probably you're best off dropping to 256MB or less.