majestyk wrote on 2022-05-28, 06:43:

Tha additional capacitor is from BE7#to Vss?

Be7# to scyc if I’m looking at it right.

There is probably a definition for those pins somewhere if you wanted to look them up. Just leave it, prob something the board designers cooked up to resolve a defect

Edit: https://www.pchardwarelinks.com/586pin.htm

Yeah, idk what is going on there 🤣

Though it does get in the way of using a tweaker. You could still use one though, just have to desolder it and put it back on top.

Anyway, from what I can see,

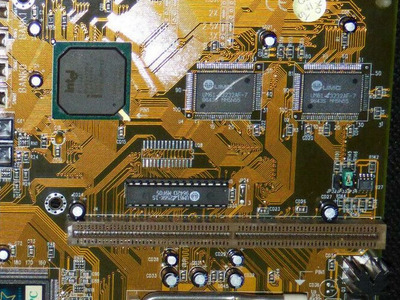

You should be able to get 512mb of ram on this board

I’m not sure though if that tag chip supports caching that much ram though. Some of these mobos will give you a bios option for that.

But the caching is a non issue with k6-3/2+/3+ Because of its onboard cache.

If you want to use another processor you may be limited to 64mb of ram if that tag ram can’t cache the 512mb.

As for your cache, I’m assuming you have 512k? Can you confirm? that’s your max anyway. Chipset doesn’t support more.

Your max fsb is as I said 66mhz unfortunately. A limitation of your clock gen. But you might be able to replace the clock gen.

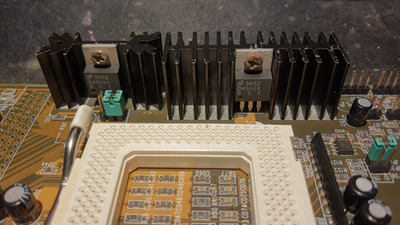

Your vrm looks like linear.

You should put a volt meter on the pin middle corner next to absent pin 1 to ground and play with your voltage jumpers. We need to know what voltages you can get there. It will tell us what cpus you can support. I suspect you’ll find a 2v or 2.2v setting. That will be sufficient.

As for multipliers, the tweaker can give you full access to all cpu supported multipliers on this mobo.

Finding working video cards for this mobo is challenging.

Many newer pci cards after geforce 4/5 stop working on 586 due to driver issues,

X800 series if they had made any pci cards for them (there is a x600 thing) but anyway it has a weird plug and dual gpus and is a mess, anway what I’m trying to say is you are looking at radeon 9000 series or geforce 4 series and below.

That cuts quite a few card out of the loop.

Next you probably need a card that works on 5v pci as most of these don’t have 3.3v

So again, more cards eliminated.

Next there is some other reason that seems to make 4 out of five cards you try not work in these.

However, there is one card that I’ve found that seems to work very well. Like seriously, I have a rage 128 that won’t even work. It’s so freakin picky

Low profile radeon 7500 pci.

Get one of those.

You can do radeon 7000 but it’s half as fast. Try to get the 7500

A close second is a radeon 9200 pro

As for sound, get a audigy 2 zs is the best performance wise probably also best quality.

You may have your preference for a isa card though but I’ve heard audigy 2zs can be made to work with dos. I know it works with 9x

As for storage: a promise sata II tx4 is a good investment for this board.

For your power supply, if you wanna use atx check out this:

ATX to AT pico Adapter! + Fan Headers Soft on/off, -5v, and 3.3v (Released)