Reply 40 of 54, by mkarcher

majestyk wrote on 2023-03-11, 11:08:Setting TAG-bit size from 8 (default) to 7 makes the difference in memory throughput performance in my case. When I set it to 7 the speedsys benchmarks are very similar to thoseCoffee One has:

I´m not sure what the reason is here, do you need 8-bit for larger RAM sizes? I only tested 64B (4 x 16M).

For L2 write-back cache to show sensible performance, you need to know whether the data in the L2 cache is newer than the data in the RAM (they call it "L2 cache is dirty"), so that when the cache should load other data, the chipset knows whether the old data from the cache needs to be written back to RAM, or it can simply be replaces. This requires one bit of storage for every data chunk in the cache ("cache line"). If you run L2 cache in write-back mode without storing this information, the chipset has to assume the worst case and always write the data from the cache back to main memory just at the moment the processor is stalled waiting for new data from the RAM to reach the processor. This operation mode is called "always dirty".

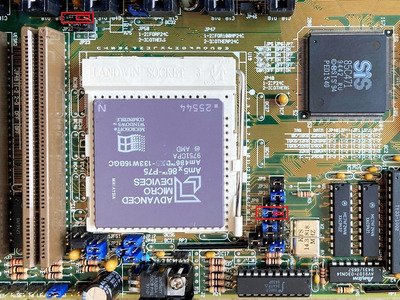

Old chipsets used a separate SRAM chip just to store the information whether a cache line is dirty (the "dirty bit" or "alter(ed) bit"). The RAM chip was called "dirty tag" or "alter tag". Modern 486 chipsets can combine the standard address tag (what has been stored in the tag RAM) and the "dirty"/"clean" information in the same 8-bit RAM chip. If you choose "TAG size: 8", the chipset uses all 8 bits for storing what part of memory is cached, and has no information about dirtyness. This is fine for L2 write-through, but causes the dreaded always-dirty mode in L2 write-back. This mode enables you to cache 64MB of RAM with 256KB of cache, 128MB of RAM with 512KB of cache or 256MB of RAM with 1MB of L2 cache. On the other hand, if you choose "TAG size: 7" (or "7+1", depending on your BIOS), only seven bits are used to know what part of memory is cached, and the eighth bit is used as "dirty"/"clean" indication. This allows sensible L2 write-back, but halves the amount of memory that can be cached.

The recommendation for genaral purpose computing is:

- Do not install more RAM than you L2 cache can cover (ctcm tests whether you have uncached memory).

- Do not use write-back mode without a dirty tag bit. If you need 8 bits for the address tag, switch L2 to write-through mode.

- If seven tag bits are enough, write-back is preferrable over write-through.

If you have the skills/tools to set aside the uncached part of RAM for "non-performance critical operation" like a RAM drive, you may install more RAM than L2 cache covers (violating the first recommendation), but if you know how to do that, you likely would have written this answer yourself 😀