First post, by red-ray

- Rank

- Oldbie

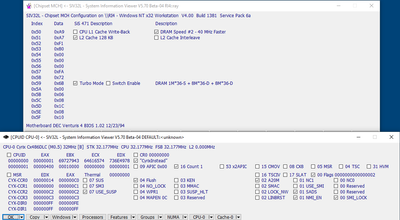

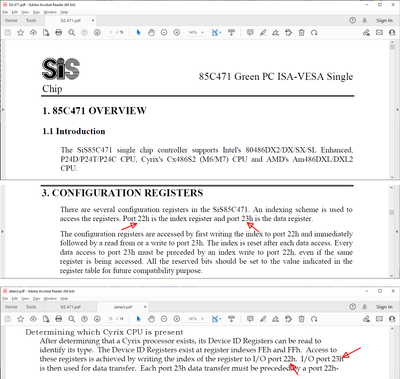

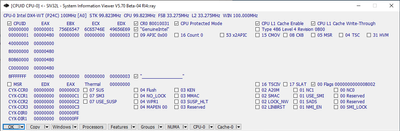

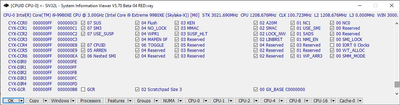

While looking at the SiS 85C471 data sheet I noted that Ports 22 + 23 are used to access the configuration registers which as you can see below are the same ports as many Cyrix CPUs use.

Given this I am wondering what will happen if a Cyrix CPU in installed in a motherboard that uses the SiS 85C471 chipset.

I am pondering getting a Cyrix 5x86 GP100, but as my DEC Venturis 4 has the SiS 85C471 chipset am wondering, will it work? I suspect it won't as the CPU will action the IOs and they will never get to the 85C471.

If you have tried this combination please can you let me know what happened? Are both the SiS 471 + Cyrix CCR + DIR registers accessible?