First post, by Masejoer

Quick question - is there any better way to better test SRAM besides a basic Xgpro SRAM test? Is there any way to write and read back X number of bits to verify that the chip is the appropriate size and functions 100%, similar to memtest verifying system RAM? Test stable cache speed?

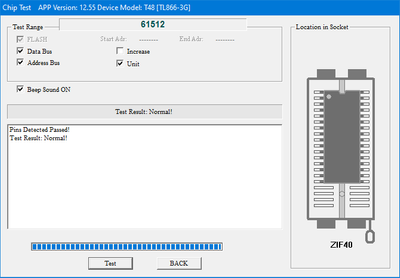

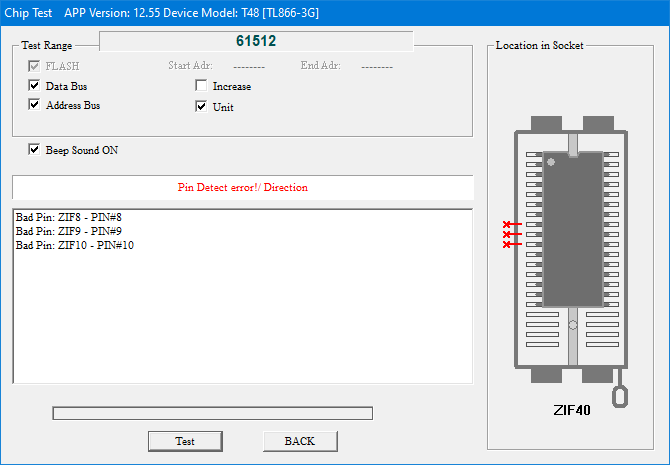

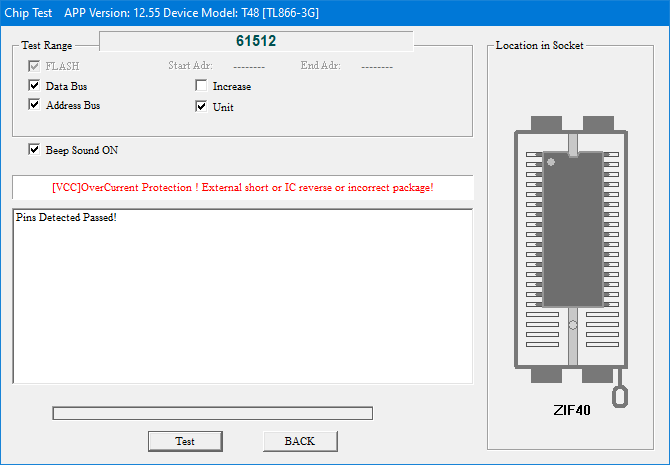

Or is the attached all we have to go off of to find obviously-bad SRAM? Just verifying things are physically good before pushing cache to the limit in a full system build?

Thanks!